实验2:1位全加器

实验目的实验原理逻辑电路(使用与非门和异或门构成)Verilog HDL建模描述实验步骤

实验任务

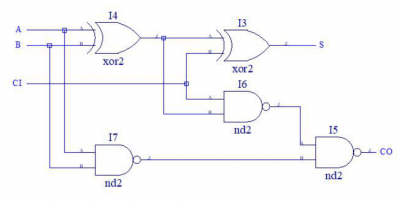

用与非门和异或门设计一个1位全加器电路,然后在实验板上实现自己设计的逻辑电路,并验证是否正确。

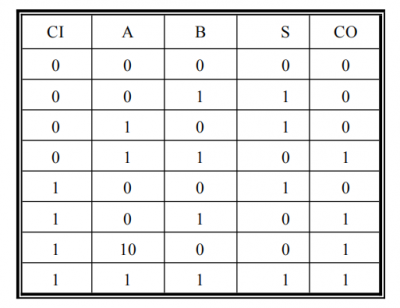

在将两个多位二进制数相加时,除了最低位以外,每一位都应该考虑来自低位的进位,即将两个对应位的加数和来自低位的进位三个数相加。这种运算称为全加,所用的电路称为全加器。按照二进制加法运算规则,可以得到如下表所示全加器真值表。其中,A、B是两个加数,CI是来自低位的进位,S是相加的和,CO是向高位的进位。将S、CO和A、B、CI的关系写成逻辑表达式则得到:

S=CI’A’B+CI’AB’+CIA’B’+CIAB=A⊕B⊕CI

CO=CI’AB+CIA’B+CI’AB’+CIAB=AB+AC+BC

1位全加器程序清单adder1.v

module adder1 (

input wire a, //输入的低位进位及两个加数cin、a、b

input wire b,

input wire cin,

output wire sum, //输出的和与进位

output wire cout );

wire s1,s2,s3; //定义中间变量

xor (s1,a,b); //调用基本异或门

xor (sum,s1,cin);

nand (s2,a,b); //调用基本与非门

nand (s3,s1,cin);

and (cout,s2,s3);

endmodule

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。

关键词:

FPGA

Lattice

Diamond

逻辑门

相关推荐

高速ADC与内置嵌入式串行收发器的FPGA接口

Lattice的3.3伏ispMACH 4000V CPLD上市

基于FPGA的可编程数字滤波器系统

FPGA如何同DDR3存储器进行接口?

以Altera可编程解决方案,驱动下一代 5G‑A与 6G 宽带射频加速演进

Altera的FPGA下载常见问题经验小结

实时的噪声源定位系统

LatticeECP3设计的视频协议板电路图-FPGA配置

用C/C++语言开发大规模FPGA [转载于www.fpga.com.cn]

Altera: 采用全系列40-nm收发器FPGA和ASIC实现创新

DC到3.2GHz采样率!PXI平台+开放FPGA赋能,我们打造了一款“软件定义”的锁相放大器

FPGA在边缘人工智能中日益扩大的作用

LabVIEW 8.20技术资料大全简介

可以解LATTICE M4A5-128/64 TQFP 吗?

人工智能开始简化可编程逻辑的设计

3-DES算法的FPGA高速实现(Xilinx)

人工智能开始简化可编程逻辑的设计流程

基于FPGA的锁相环位同步提取电路

发力物理AI:Altera以FPGA创新,赋能机器人及边缘场景

贸泽电子开售:面向工业、AI、医疗、数据中心等领域的Altera Agilex 5 FPGA与SoC

基于SD7502构成的FPGA-ASK电路图

即使在汽车中,基本的逻辑功能依然是必需的

LabVIEW FPGA 模块简介

ALTERA的PCI_IP Core问答集

弥合传感器融合鸿沟:FPGA如何助力边缘端实时机器人应用

可以解LATTICE M4A5-128/64 TQFP 吗?

Altera公司cyclone系列FPGA-1C6电路图

可以解LATTICE M4A5-128/64 TQFP 吗?

利用锚定可信平台模块(TPM)的FPGA构建人形机器人安全

视频协议板-FPGA配置基于LatticeECP3的设计