自2005年9月LXI总线推出以来,已经显示出其组建测试系统的众多优点。基于LXI总线组建测试系统具有易于使用、灵活性高、模块化和可扩缩性、实现更快的系统吞吐率、可分布式应用、长寿命、低成本、通过IEEE1588时钟同步、机架空间小、合成仪器等诸多优点。

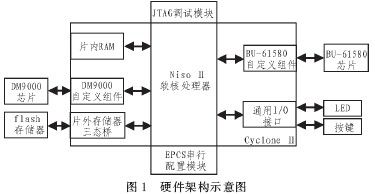

1553B总线的全名为“时分制指令/响应式多路传输数据总线”,国内多型战斗机、军舰等武器平台都采用其作为传输总线。因此研制基于LXI总线的1553B通讯模块,不仅能满足多型武器装备对1553B总线的测试需求,也对LXI总

关键字:

NiosⅡ 1553B FPGA

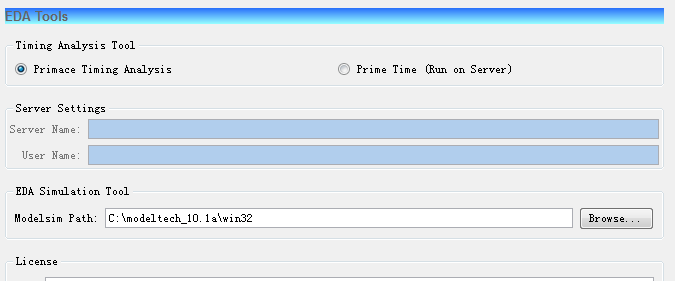

京微雅格是世界上除美国硅谷以外唯一自主研发并成功量产现场可编程逻辑(FPGA)芯片的公司,目前拥有数百项技术专利和近百款产品。目前,已经有越来越多的用户都开始使用国产FPGA来做自己的设计,然而在FPGA的开发过程中,免不了要对设计进行仿真。京微雅格的FPGA是支持在modelsim中进行仿真的。

京微雅格的FPGA需要在Primace软件中进行开发,为了便于客户进行仿真设计,在Primace5.0及以上版本都支持在工程中直接调用仿真工具Modelsim。同时,也支持在modelsim中直接进行

关键字:

京微雅格 FPGA 仿真

Spartan-3 FPGA能以突破性的价位点实现嵌入式DSP功能。本文阐述了Spartan-3 FPGA针对DSP而优化的特性,并通过实现示例分析了它们在性能和成本上的优势。

所有低成本的FPGA都以颇具吸引力的价格提供基本的逻辑性能,并能满足广泛的多用途设计需求。然而,当考虑在FPGA构造中嵌入DSP功能时,必须选择高端FPGA以获得诸如嵌入式乘法器和分布式存储器等平台特性。

Spartan-3 FPGA的面世改变了嵌入式DSP的应用前景。虽然Spartan-3系列器件的价位可能较低,

关键字:

赛灵思 FPGA Spartan-3

横跨多重电子应用领域、全球领先的半导体供应商意法半导体(STMicroelectronics,简称ST)宣布对基于射线跟踪 (ray-tracing) 技术的实验性3D图形应用系统进行测试验证。该解决方案采用一颗与现场可编程门阵列 (FPGA, Field-Programmable Gate Array) 相连、基于ARM®处理器的测试芯片。FASTER 研发项目以“简化分析合成技术,实现有效配置”为目标,是意法半导体与米兰理工大学 (Politecnico di Mi

关键字:

意法半导体 FPGA GPU

一、Altera Quartus II 11.0套件介绍

所谓巧妇难为无米之炊,再强的软硬件功底,再多的思维创造力,没有软件的平台,也只是徒劳。因此,一切创造的平台——Quartus II 软件安装,由零开启的世界,便从此开始。

自从Bingo 2009年开始接触FPGA,Quartus II 版本的软件从n年前的5.1版本到今天的最新发布的11.0,都使用过;当然对于软件核心构架而言,万变不离其宗。虽然多多少少有点bug,但这10多个版本发展到了现在,能看到Alt

关键字:

FPGA Quartus II

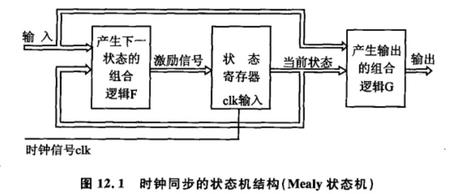

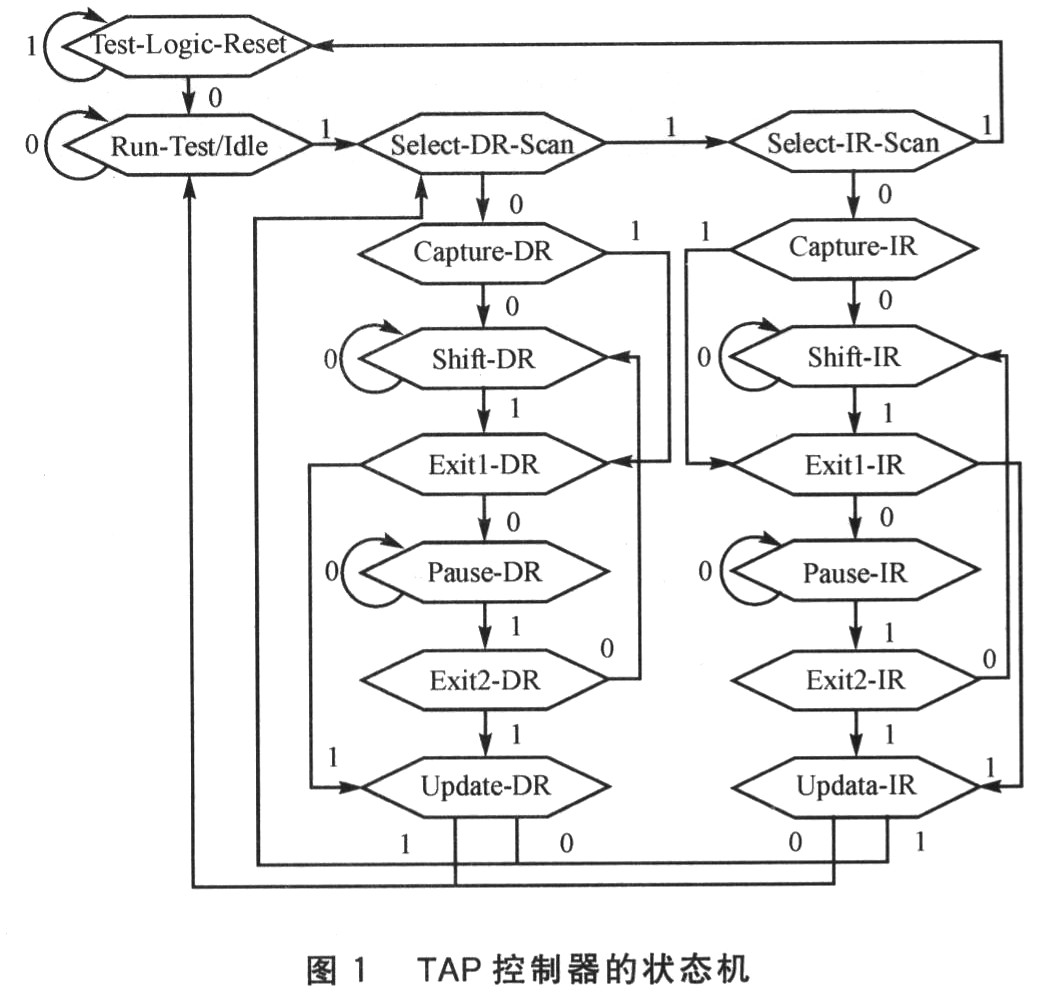

今天我们来写状态机。

关于状态机呢,想必大家应该都接触过,通俗的讲就是数电里我们学的状态转换图。状态机分为两中类型,一种叫Mealy型,一种叫Moore型。前者就是说时序逻辑的输出不仅取决于当前的状态,还取决于输入,而后者就是时序逻辑的输出仅仅取决于当前的状态。下面两个图分别表示两种不同的状态机。

下面我们就通过代码来写一下状态机,以下面的状态转换图为例

首先,是一种典型的状态机写法,这种写法我们称为

关键字:

FPGA 状态机 Mealy Moore

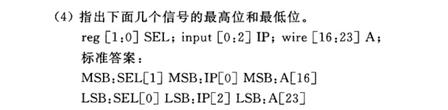

习题呢,来自夏雨闻老师的那本教材,就挑几个感觉自己做着有点难度的写写吧

这个题呢刚开始我是没看明白,记得书上只讲了我们习惯上的用法,这种用法我是没见过,问了下别人才知道,Verilog中一般是左高右低。第一个没问题,第二个,input [0:2] IP,习惯上我们这样写 input [2:0] IP,这里两个是等价的,即表示第0 .1 .2 三位。第三个,wire [16:23] A,也是,左高右低,表示第16.17.....22. 23位,左高右低就这样记就好了。

关键字:

FPGA 夏雨闻 寄存器

Xilinx公司的MicroBlaze 32位软处理器核是支持CoreConnect总线的标准外设集合。MicroBlaze处理器运行在150MHz时钟下,可提供125 D-MIPS的性能,非常适合设计针对网络、电信、数据通信和消费市场的复杂嵌入式系统。

1 MicroBlaze的体系结构

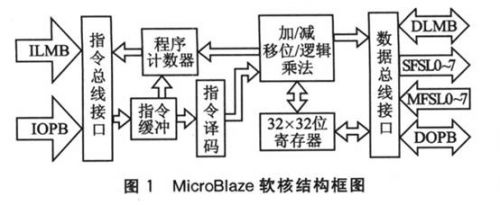

MicroBlaze 是基于Xilinx公司FPGA的微处理器IP核,和其它外设IP核一起,可以完成可编程系统芯片(SOPC)的设计。MicroBlaze 处理器采用RISC架构和哈佛结构的32位指令和

关键字:

MicroBlaze Xilinx FPGA

1 引言

由于Internet技术的渗透,嵌入式系统正变得越来越智能化并具有越来越多的网络友好特性。Web技术的飞速发展,给嵌入式系统进入Internet提供绝佳的途径。在现场仪表和企业设备层应用嵌入式技术是企业监控系统的发展趋势。与现场总线技术相比,嵌入式技术不仅为开发者提供了大量的工具和函数库,而且减少了传统的客户端,减少了二次开发的工作量;而把嵌入式技术和Internet技术结合起来,使得整个工控网络易于和Internet实现无缝连接;现在多数企业控制网络是通过专用线路进行数据通信,其通信

关键字:

MicroBlaze Xilinx FPGA

1 MicroBlaze的体系结构

MicroBlaze采用功能强大的32位流水线结构,包含32个32位通用寄存器和1个可选的32位移位器,时钟频率可达150 MHz;在Virrex一4 FPGA上运行速率高达120 DMIPS,仅占用Virtex—II Pro FPGA中的950个逻辑单元。MicroBlaze软核的结构框图如图1所示。它具有以下基本特征:

①32个32位通用寄存器和2个专用寄存器(程序计数器和状态标志寄存器)。

②32位指令系统,支持3个操作数和2种寻

关键字:

MicroBlaze GPIO FPGA

引 言

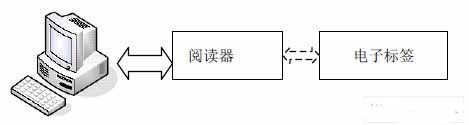

RFID 技术是从 20 世纪 80 年代走向成熟的一项自动识别技术,近年来发展十分迅速。 目前,在全世界,基于 RFID 技术的电子标签,使用已经 非常广泛了,这主要取决于它的特性,RFID 标签可以使用在几乎所有的物理对象上。RFID 技术在 工业自动化,物体跟踪,交通运输控制管理,防伪校园卡,电子钱包,行李标签,收费系统,医用装 置,电子物品的监控和军事用途等方面已经得到了广泛的应用。例如第二代居民身份证,使用基于 ISO/IEC4443-B 标准的 13.56 MHz 电子标签,

关键字:

Microblaze RFID阅读器 FPGA FIFO

SOPC技术的发展,给仿真器指出了新的发展方向。所谓SOPC技术,就是指用可编程技术将整个系统放在一块硅片上。在传统设计中电路级相互独立的各个系统被集成到一块FPGA芯片中。

SOPC的可重用性是一种先进的设计思想。为了降低用户的负担,避免重复劳动,将一些在数字电路中常用但比较复杂的功能模块,比如SDRAM控制器等,设计成可修改参数的模块,用户在设计系统时可以直接调用这些模块。这些特定的功能模块被称为IPcore(知识产权核)。由于IPcore通常是很成熟的,因此降低了开发风险。

本文利用

关键字:

SOPC JTAG FPGA

引言

针对需要切换多个FPGA配置码流的场合, Xilinx公司提出了一种名为System ACE的解决方案,它利用CF(Compact Flash)存储卡来替代配置用PROM,用专门的ACE控制芯片完成CF卡的读写,上位机软件生成专用的ACE文件并下载到CF存储卡中,上电后通过ACE控制芯片实现不同配置码流间的切换[1]。

System ACE的解决方案需要购买CF存储卡和专用的ACE控制芯片,增加了系统搭建成本和耗费了更多空间,而且该方案只能实现最多8个配置文件的切换,在面对更多个配置

关键字:

Flash JTAG FPGA

“FPGA目前非常火,各个高校也开了FPGA的课程,但是FPGA并不是每个人都适合,FPGA讲究的是一个入道,入什么道,入电子设计的道,就是说,这个过程,你得从电子设计开始,然后再学FPGA,而不是先从VHDL/Verilog开始,直接跳过数电模电。这一点非常重要,这涉及到你以后的发展高度的问题。我是过来人,我深刻体会到FPGA与数电模电的基础的深层次联系。对于本科生而言,你可以把FPGA当作业余兴趣,但不要把它当成今后的饭碗,你可以保持这个兴趣直到研究生读完。从我招聘的情况来看,做FPG

关键字:

FPGA Verilog SRAM

Altera公司今天宣布,奥迪的高级辅助驾驶系统(ADAS)选用其SoC现场可编程门阵列(FPGA),实现量产。奥迪是自动驾驶汽车技术的领先者,奥地利高科技公司TTTech则是奥迪中央辅助驾驶控制单元zFAS的核心开发合作伙伴,他们选择了Altera® Cyclone® V SoC FPGA帮助提高其系统性能,突出奥迪在导航驾驶和驻车方面的优势,而这些是专用标准产品(ASSP)解决方案无法实现的。

Altera的Cyclone V SoC FPGA结合了可编程逻辑和双核ARM C

关键字:

Altera SoC FPGA

spartan.fpga介绍

您好,目前还没有人创建词条spartan.fpga!

欢迎您创建该词条,阐述对spartan.fpga的理解,并与今后在此搜索spartan.fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473