零基础学FPGA(七)浅谈状态机

今天我们来写状态机。

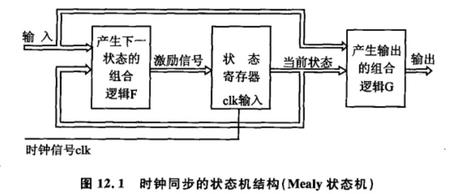

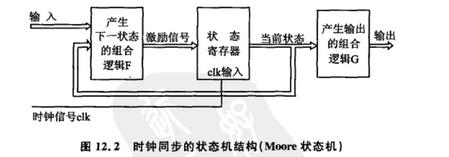

本文引用地址:https://www.eepw.com.cn/article/267960.htm关于状态机呢,想必大家应该都接触过,通俗的讲就是数电里我们学的状态转换图。状态机分为两中类型,一种叫Mealy型,一种叫Moore型。前者就是说时序逻辑的输出不仅取决于当前的状态,还取决于输入,而后者就是时序逻辑的输出仅仅取决于当前的状态。下面两个图分别表示两种不同的状态机。

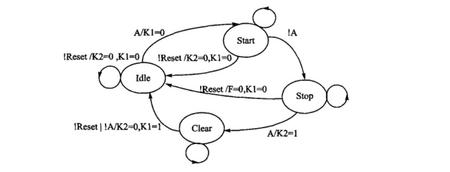

下面我们就通过代码来写一下状态机,以下面的状态转换图为例

首先,是一种典型的状态机写法,这种写法我们称为一段时状态机,用于一些简单的设计是可以的,但如果是复杂的状态机,不建议大家用这种写法。

//***********************************************************

//可综合的状态机设计的典型方法

//实现典型的状态机设计

//**********************************************

module fsm (clk,rst_n,A,k1,k2,State);

input clk;

input rst_n;

input A;

output k1,k2;

output [1:0] State;

reg k1;

reg k2;

reg [1:0] State; //当前状态寄存器

parameter Idle = 2'b00,

Start = 2'b01,

Stop = 2'b10,

Clear = 2'b11; //编码 ,注意,只有在最后一句用分号,其他地方用逗号

always @(posedge clk or negedge rst_n)

if(!rst_n)

begin

State <= Idle;

k1 <=1'b0;

k2 <=1'b0;

end

else case (State) //状态判断与组合逻辑赋值

Idle :if(A) begin

State <= Start;

k1 <= 0;

end

else begin

State <= Idle;

k1 <= 0;

k2 <= 0;

end

Start :if(!A) State <= Stop;

else State <= Start;

Stop :if(A) begin

State <=Clear;

k2 <= 1;

end

else State <= Stop;

Clear :if(!A) begin

State <= Clear;

k2 <= 0;

k1 <= 1;

end

else State <= Clear;

default : State <= 2'bxx; //告诉综合器 case语句已经指定了所有状态,这样综合器就会删除不需要的译码电路,使生成的电路简单

endcase

endmodule

fpga相关文章:fpga是什么

评论