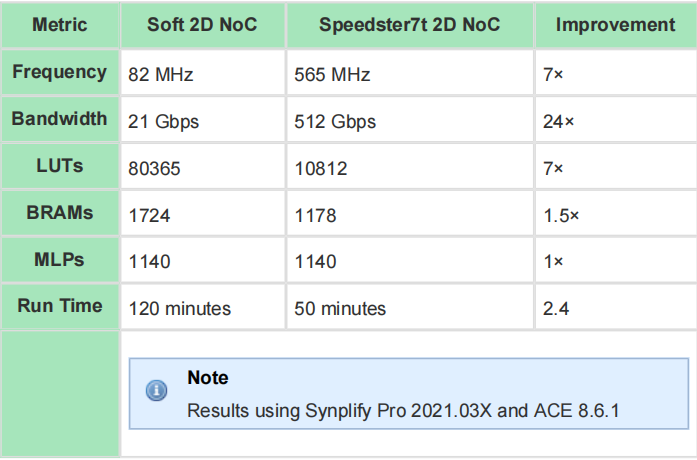

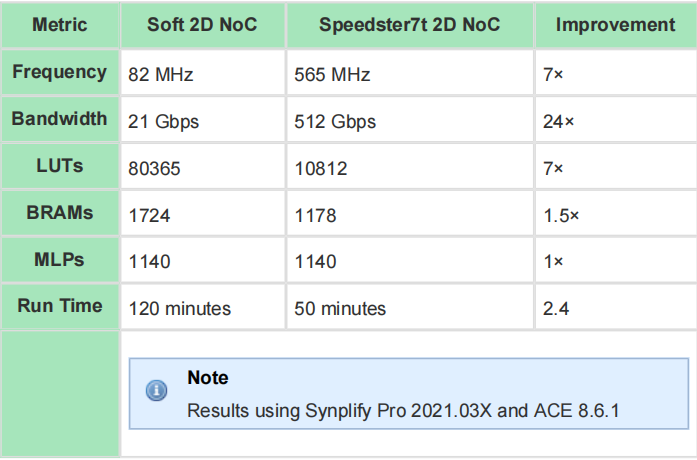

- 摘要随着旨在解决现代算法加速工作负载的设备越来越多,就必须能够在高速接口之间和整个器件中有效地移动高带宽数据流。Achronix的Speedster®7t独立FPGA芯片可以通过集成全新的、高度创新的二维片上网络(2D NoC)来处理这些高带宽数据流。Achronix的FPGA中特有的2D NoC实现是一种创新,它与用可编程逻辑资源来实现2D NoC的传统方法相比,有哪些创新和价值呢?本白皮书讨论了这两种实现2D NoC的方法,并提供了一个示例设计,以展示与软2D NoC实现相比,Achronix 2D

- 关键字:

Achronix FPGA 2D NoC

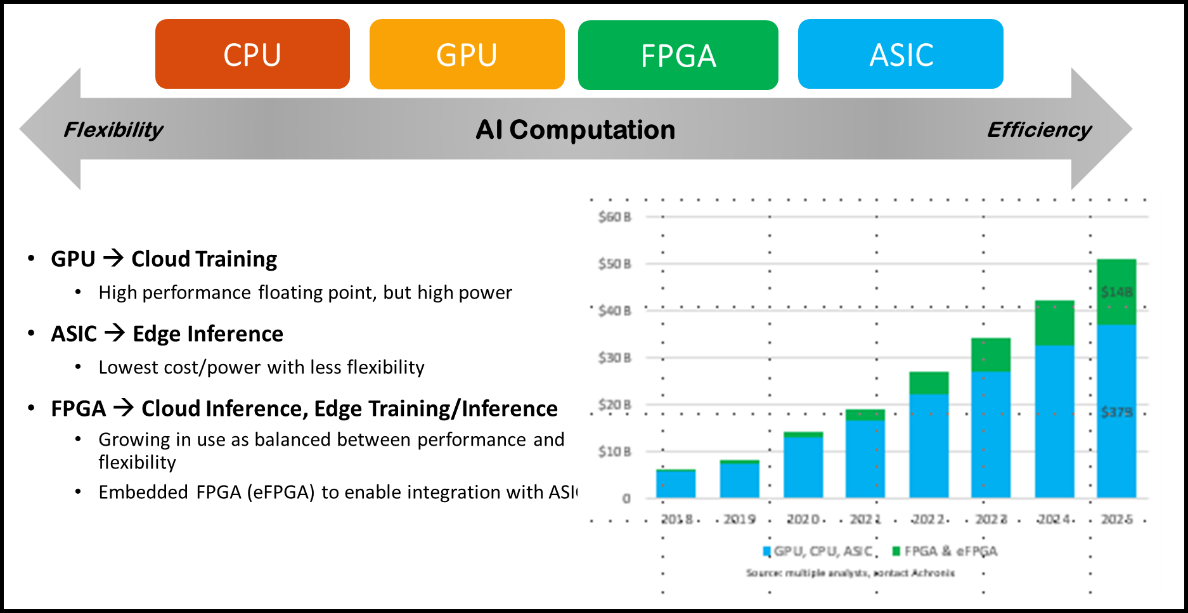

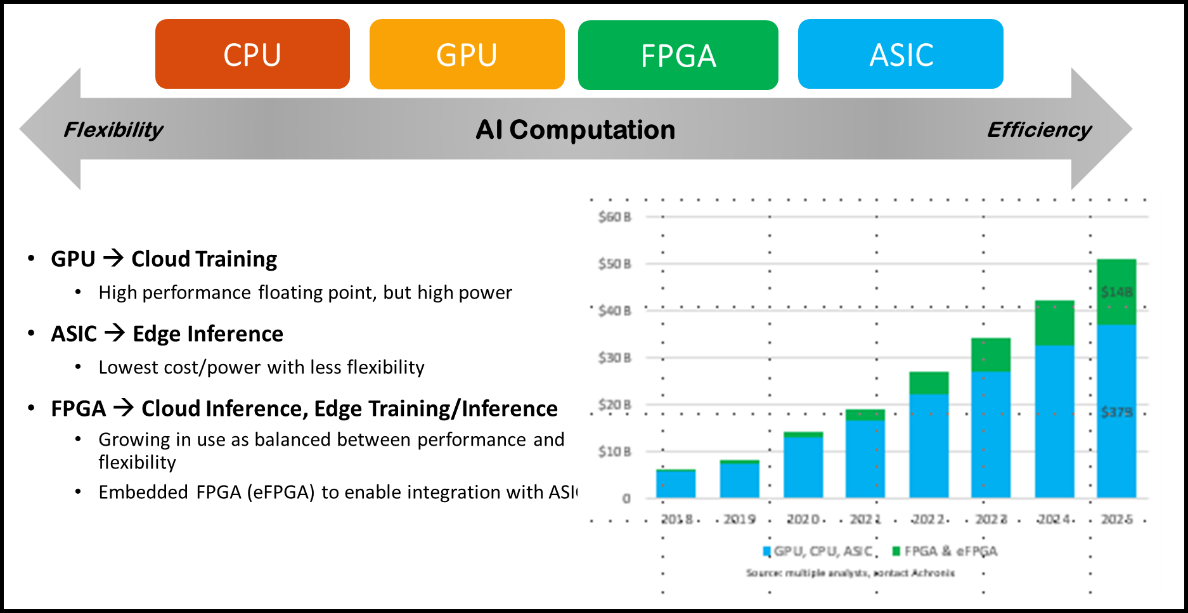

- 四大类人工智能芯片(GPU、ASIC、FGPA、类脑芯片)及系统级智能芯片在国内的发展进度层次不齐。用于云端的训练、推断等大算力通用 芯片发展较为落后;适用于更多垂直行业的终端应用芯片如自动驾驶、智能安防、机器人等专用芯片发展较快。超过80%中国人工智能产业链企 业也集中在应用层。 总体来看,人工智能芯片的发展仍需基础科学积累和沉淀,因此,产学研融合不失为一种有效的途径。研究主体界定:面向人工智能领域的芯片及其技术、算法与应用无芯片不AI , 以AI芯片为载体实现的算力是人工智能发展水平的重要衡

- 关键字:

AI芯片 GPU ASIC FPGA 行业研究

- 高性能现场可编程逻辑门阵列(FPGA)和嵌入式FPGA(eFPGA)半导体知识产权(IP)领域的领导性企业Achronix半导体公司宣布:公司已任命江柏汉先生为全球销售副总裁。江先生为Achronix带来了超过30年的半导体产品销售经验,并将领导Achronix全球销售组织体系。在加入Achronix之前,江先生曾在Marvell半导体公司担任销售副总裁兼中国区总经理并常驻上海。在Marvell,江先生通过赢得一些战略性的项目和提高市场份额,成功地加快了公司业务的增长,同时对多项收购和资产剥离进行了整合和

- 关键字:

Achronix FPGA

- 莱迪思半导体宣布其CrossLink-NX FPGA和专为AI优化的软件解决方案,将用于联想最新的ThinkPad X1系列笔记本电脑中。全新的联想ThinkPad产品系列采用莱迪思充分整合的客户端硬件和软件解决方案,能够在不损失效能或电池使用时间的情况下提供优化的使用者体验,包括沉浸式互动、更好的隐私保护和更高效的协作。 莱迪思FPGA助力联想新一代网络边缘AI体验莱迪思营销和业务发展副总裁Matt Dobrodziej表示:「我们的AI优化解决方案产品旨在满足希望实现更高智能的各种网络边缘应

- 关键字:

莱迪思 FPGA 联想 边缘AI

- 针对固体火箭发动机推进剂药柱应变量大、高频振动时应变不易测量的问题,基于FPGA和柔性应变计设计了柔性应变测量装置。柔性应变计的测量范围大,可以测量双向应变,解决了推进剂药柱应变测量的难题。FPGA具有实时性高、并行运行的优点,解决了多路应变实时采集的难题。该应变测量装置还可用于其他高分子材料的应变测量。

- 关键字:

推进剂 柔性应变计 FPGA 高频振动 高速采集 202111

- 1 为什么AI/ML发展如此迅速?多年来,人工智能(AI)/机器学习(ML)市场一直以指数级的速度快速增长,其解决方案遍布我们周围,从机器人和其他机械系统的预测故障算法、电子商务中的购买行为建议、自动驾驶车辆的目标检测、电子交易中的风险缓解到DNA测序等等,我们身边有各种各样的解决方案,示例不胜枚举。那么,为什么AI/ML发展如此迅速呢?据IDC、Gartner和其他市调机构的分析,全球大约80%的数据是非结构化数据。电子邮件、照片、语音邮件、视频和许多其他数据源每天都在堆积。无论

- 关键字:

AI 机器学习 FPGA

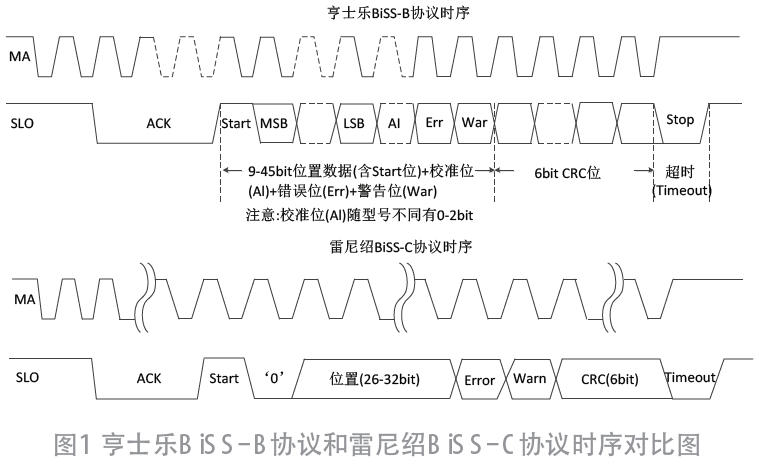

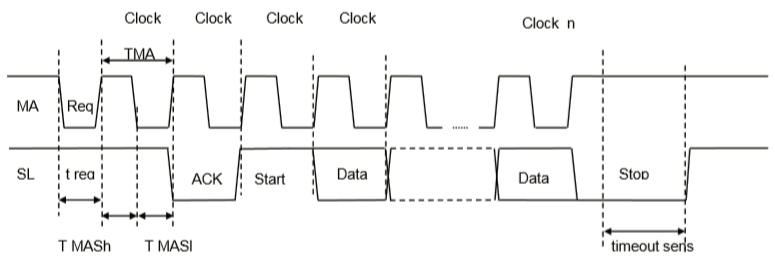

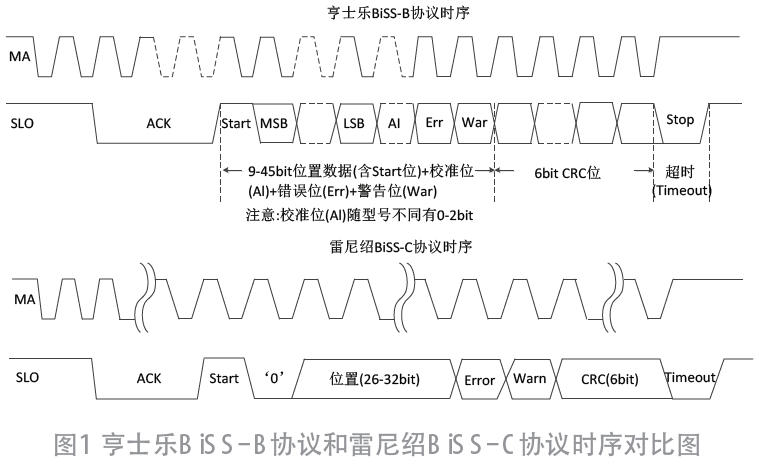

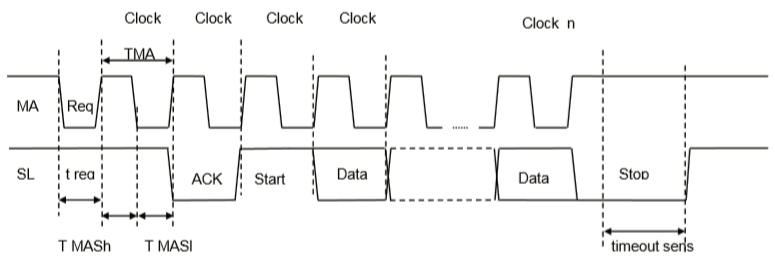

- BiSS协议是一种高速同步串行通信协议,使用BiSS协议的编码器有利于提高伺服控制系统的动态性能,在高精度绝对式编码器中应用广泛。本文在分析BiSS协议数据帧特点的基础上,利用FPGA设计了BiSS协议编码器解码器,采集了BiSS协议编码器位置数据和总线波形,通过与DSP联合使用,基于BiSS协议编码器对永磁同步电机的动态性能进行了验证,结果表明该设计的合理性。

- 关键字:

BiSS FPGA 编码器 DSP 202108

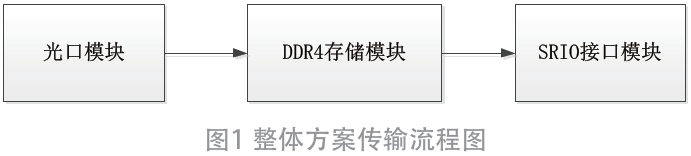

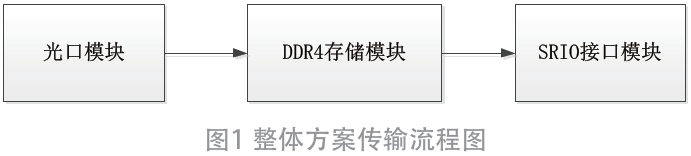

- 5G通信的主要特征包括“高速率、大带宽”,为了满足高速率、大带宽数据的传输要求,需要一种存储技术对数据进行存储。本文就存储技术结合DDR4协议,设计了一种DDR4传输机制,本研究采用高性能的XCVU9P系列的FPGA芯片作为控制芯片,使用其内部自带的DDR4 SDRAM(MIG)IP核进行例化核设计。经过验证,实现在250 MHz时钟下对DDR4 SDRAM的读/写操作,数据无丢失,能够保证高速率、大带宽数据正常传输,该传输机制具有良好的可靠性、适用性及有效性。

- 关键字:

DDR4 高速率 大带宽 FPGA 202108

- 针对5G毫米波通信宏基站、微基站等设备的研发、生产、预认证、维修保障等测试需求,设计一款可应用于“5G新基建”通信设备产业链多环节所需仪表的高效多速率信号接收机处理模块。采用先进的并行多相滤波技术和任意速率比FFT处理技术,基于FPGA算法平台实现毫米波5G接收机多路信号接收时域/频域并行变速率处理逻辑电路,提高5G复杂波形接收机信号解析的实时性。实验结果表明,该电路能高效完成5G复杂波形接收机信号的时域/频域解析,适合作为毫米波5G接收机多速率数据处理实施方案,满足毫米波5G接收机的功能设计要求。

- 关键字:

FPGA 5G 毫米波 接收机 202105

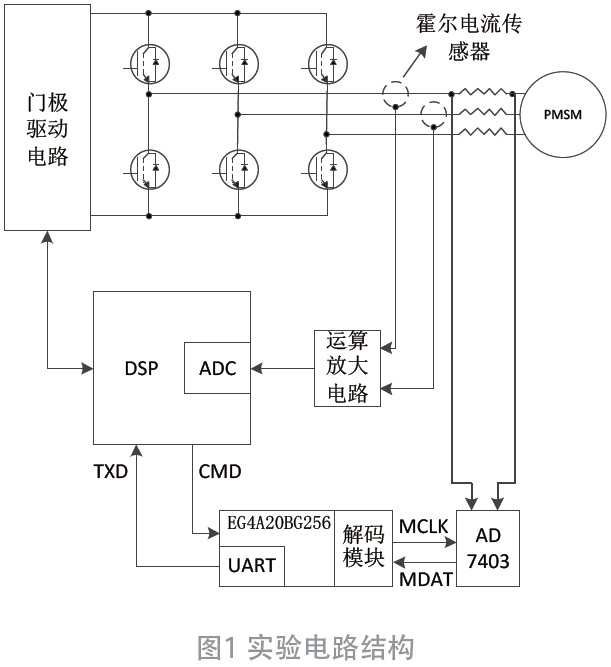

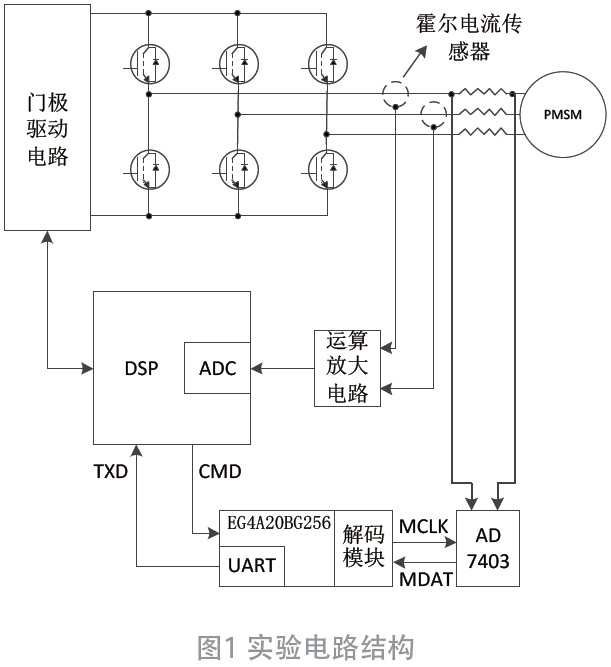

- AD7403是一种Σ-Δ型模数转换器,广泛应用于需要电气隔离的伺服控制电机相电流采集场合。EG4A20BG256是一种国产FPGA,适用于伺服控制系统信号采集﹑接口扩展等应用场景。本文基于EG4A20BG256 FPGA设计了AD7403模数转换器接口电路,采集永磁同步电机相电流,并与伺服控制电路内霍尔电流传感器和DSP采样结果进行了对比。结果表明,EG4A20BG256 FPGA可以通过AD7403模数转换器实现对永磁同步电机相电流的准确采集。

- 关键字:

AD7403 EG4A20BG256 FPGA DSP 永磁同步电机 202105

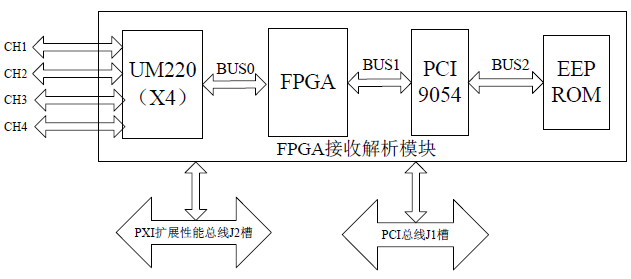

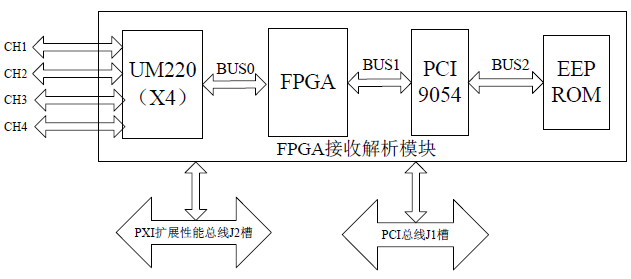

- 设计并实现了一种BD/GPS卫星导航信号多通道隔离转换测量显示系统。该系统将一路输入的BD/GPS信号通过功分器转换为等量的四路隔离输出信号,经FPGA解析后实时显示在电脑屏幕上,为BD/GPS信号的使用提供直观的数据基础。

- 关键字:

BD/GPS FPGA 功分器 隔离 202107

- 摘要:针对目前BiSS协议编码器数据读取多采用FPGA实现的实际情况,文中介绍一种基于XMC4500微控制器的BiSS协议编码器数据读取实现方案。采用该方案,可将使用BiSS协议编码器的伺服系统控制电路常用的DSP+FPGA双控制器架构方式简化为XMC4500单控制器方式,在一定程度上降低了硬件成本和开发难度。用该方案采集BiSS协议编码器数据的实物平台,使用LabVIEW显示对读取的数据,并与电机自带增量编码器值进行对比,同时记录BiSS协议编码器实际数据波形图,结果表明,该方案具有较高的采样速率和较好

- 关键字:

202106 BiSS XMC4500 DSP FPGA LabVIEW

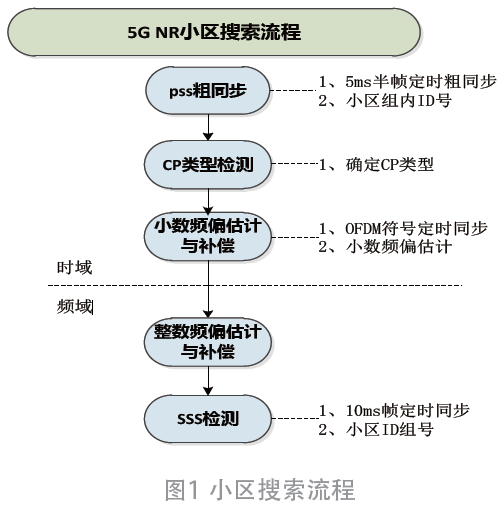

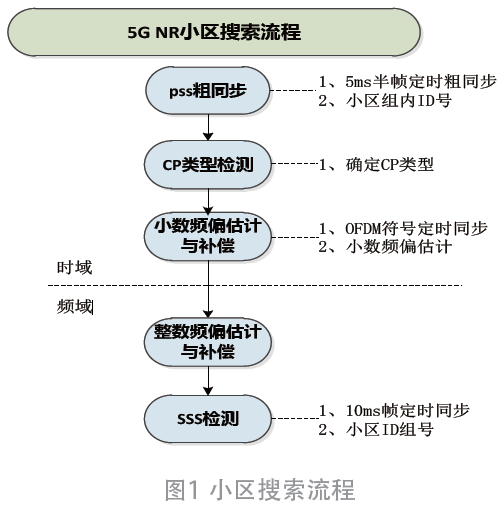

- 随着移动通信的高速发展,5G NR通信已经进入我们的日常生活,5G系统对信息传输制订了全新标准,基于5G NR的小区搜索相对于长期演进(LTE)而言,对同步信号进行了重新定义。文章详细分析了5G NR系统的主辅同步信号(PSS&SSS),对其新增内容进行了研究,提出了适用于5G NR系统的小区搜索算法,使用MATLAB软件对该算法的性能进行了仿真分析,最后在FPGA上实现开发应用。

- 关键字:

5G NR FPGA 小区搜索 PSS SSS 202105

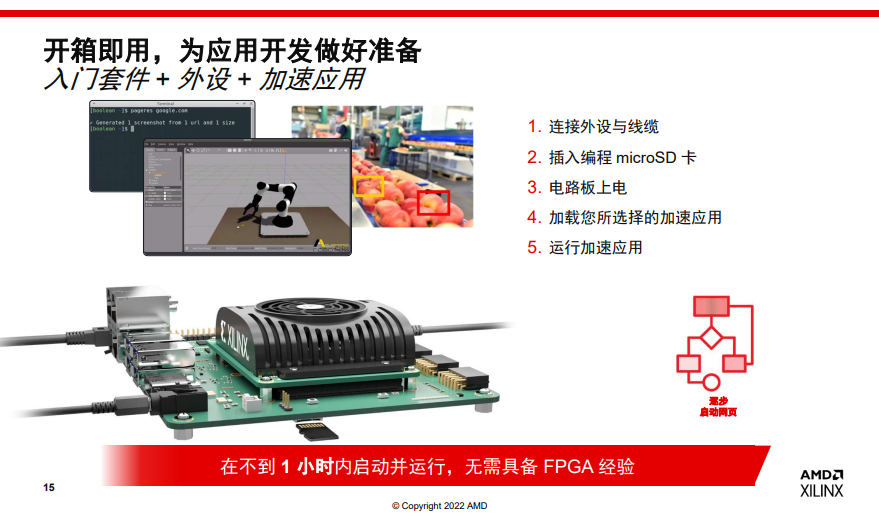

- 边缘运算主要包含以下四个部分,低时延、AI算力、低功耗以及安全和保密,这四者是边缘自主非常重要的组成部分,也是边缘区别于工业和IoT的一个主要特点,也就是用运算资源来支持边缘的自主,使它能够独立于云端。 赛灵思Versal AI Edge系列资深产品线经理 Rehan Tahir赛灵思Versal AI Edge系列高级产品线经理Rehan Tahir指出,当赛灵思在2018年引入Versal ACAP的时候,首先推出的是Versal Core和Prime系列,用于云端和网络,然后推出了Vers

- 关键字:

赛灵思 FPGA ADAS

fpga介绍

FPGA是英文Field-Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、EPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个新概念,内部包括可 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473