基于EG4A20BG256和AD7403的电流采样电路设计

作者简介:李绍军(1989—),男,硕士,工程师,研究方向为光电云台伺服。

本文引用地址:https://www.eepw.com.cn/article/202108/427286.htm0 引言

永磁同步电机电流环是永磁同步电机控制系统速度环和位置环的基础,对控制系统实现快速响应﹑提高动态性能有重要的影响。电流环的实现依靠模数转换电路完成对电机相电流的采集,在很多电机驱动场合,出于降低干扰提高采样精度或是保证电路安全的考虑,需要在驱动电路和信号处理电路间有电气隔离,常见的隔离式电流采集电路有三种基本形式:霍尔电流传感器结合运算放大器﹑采样电阻结合隔离式运算放大器﹑采样电阻结合Σ-Δ型模数转换器 [1]。前两种方式一般需要结合电机驱动电路控制器(如DSP)的ADC 外设进行处理,后者则需要通过 FPGA 或具有Δ-Σ调制器的控制器进行处理。电流环会对采集到的电流进行一系列的数学运算处理,相比DSP 串行运算结构,FPGA 的并行运算结构可减小电流环路延时,提高电流环带宽,进而提高速度环响应速度[2]。在需要过采样以及高于16 bit 分辨率的模数转换器的应用领域,Σ-Δ型模数转换器相比传统逐次逼近式模数转换器具有很大优势,应用也更为广泛[3]。文中通过国产EG4A20BG256 FPGA 结合采样电阻以及Σ-Δ型模数转换器对永磁同步电机相电流进行了采样,并同时采样了霍尔电流传感器结合运算放大器的结果,以便对采样结果进行分析对比。

1 硬件设计

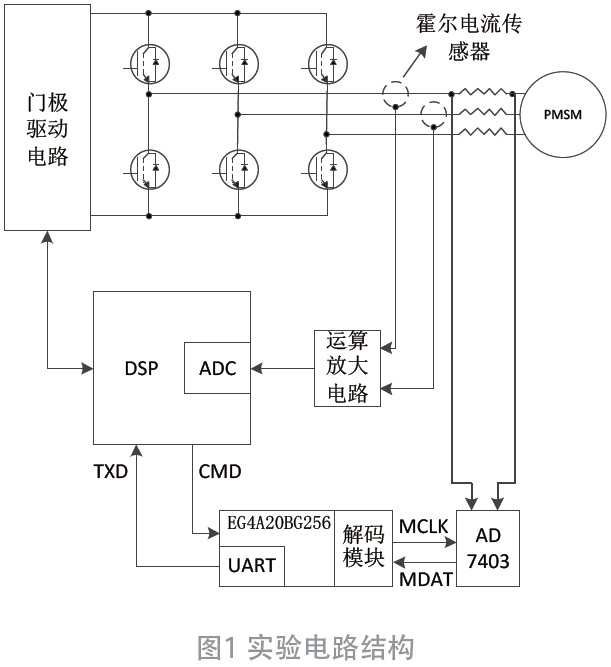

实验电路组成结构如图1 所示。DSP 通过门极驱动电路与三相桥电路驱动永磁同步电机匀速转动,AD7403-8 为AD7403 的8 脚封装, 通过采集永磁同步电机电枢回路采样电阻端电压,输出数字码流给EG4A20BG256 FPGA 解码处理,处理结果发送给DSP;同时DSP 通过霍尔电流传感器采集永磁同步电机相电流,并经运算放大电路信号调理后通过其内部ADC 模块进行采集作为对比样本。

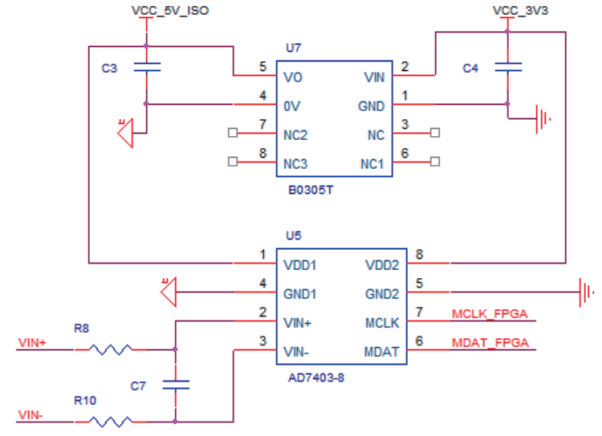

EG4A20BG256 是安路科技推出的一款EAGLE 系列国产低成本FPGA,有19 600 个LUT 单元﹑ 156 800 kbit存储器﹑ 196 个用户I/O 口﹑ 4 个PLL ﹑还有1 个ADC模块和多个LVDS 接口,非常适合伺服控制应用领域[4]。AD7403 是一款高性能数字隔离式模数转换器,内置二阶Σ-Δ型调制器,可以将模拟信号转换为高速单个位数据流,满输入量程为± 320 mV,可通过调整输入端采样电阻的大小实现采样电流量程的灵活调整。AD7403-8 采样电路如图2 所示。其两侧供电电源相互独立隔离,右侧3.3 V 电源与B0305T 隔离式电源转换器共用,左侧5 V 隔离电源由B0305 输出提供。左侧VIN+ 和VIN- 引脚通过差分滤波电路采集电机电枢回路采样电阻两端的端电压。AD7403-8 将采样电压转换为一组占空比与电压值相关的码流,接收EG4A20BG256 FPGA 提供的码流时钟,并将码流发送至FPGA 处理。

图2 AD7403-8采样电路

2 软件设计

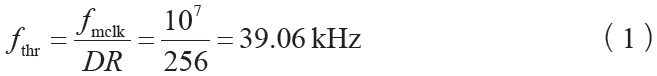

Σ-Δ型模数转换器工作的基本思想是采用高速﹑低位数(如1 位)的模数转换器来实现低速﹑高位数的模数转换器[5]。AD7403-8 内部通过二阶调制器将采样电压转换为对应的数字码流,为重构原始电压信息,EG4A20BG256 FPGA 需要使用sinc3 滤波器对该码流进行数字滤波和抽取处理。抽取率与模数转换器吞吐速率和输出数据位数相关,本次使用的码流滤波解码模块抽取率为256,AD7403-8 输入时钟设置为10 MHz,则其最大数据吞吐速率为:

其中,fmclk 为模数转换器输入时钟,DR 为抽取率;

最大转换位数为:

![]()

其中,N为sinc 滤波器阶数,此处取值为3,DR为抽取率;

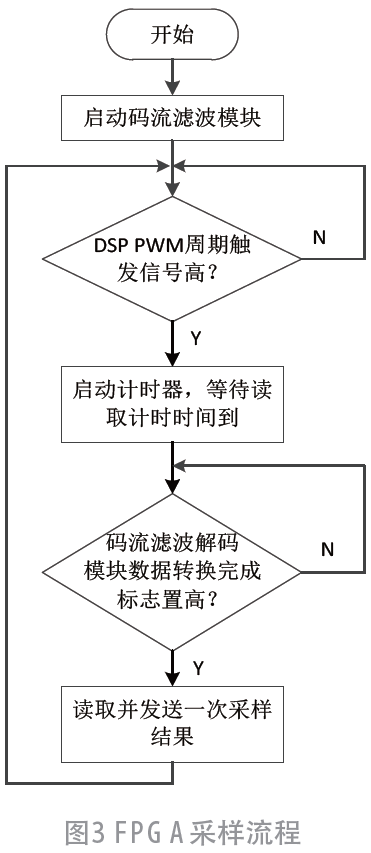

此处仅取高16 bit 作为转换结果。上电后FPGA 启动码流滤波模块,由于需要和DSP 采样结果进行对比,FPGA 采样时刻需要与DSP 输出PWM 周期进行同步匹配,当到其PWM 周期时,将FPGA 采样触发信号置高并发送给FPGA;FPGA 启动延时直到延时时间到达后启动采样,保证FPGA 与DSP 在PWM 周期中心时刻同步进行采样;待滤波解码模块输出完成标志后,将采样结果通过串口发送至DSP。DSP 输出PWM 频率设置为10 kHz,当前AD7403-8 最大吞吐速率远高于PWM频率,可满足采样需求,FPGA 工作流程如图3 所示。

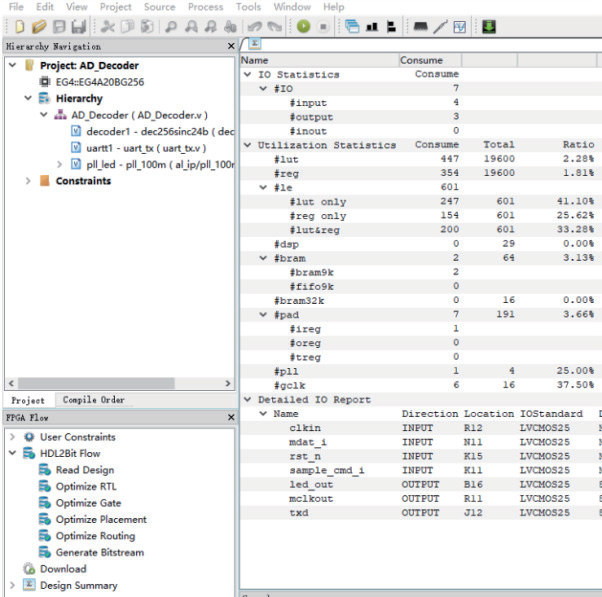

FPGA 开发环境为Anlogic TD 5.0.2 64-Bit,FPGA资源消耗情况如图4 所示。

图4 FPGA资源消耗

3 实验分析

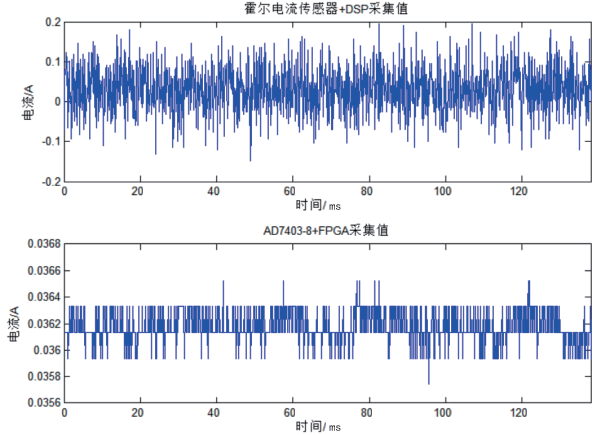

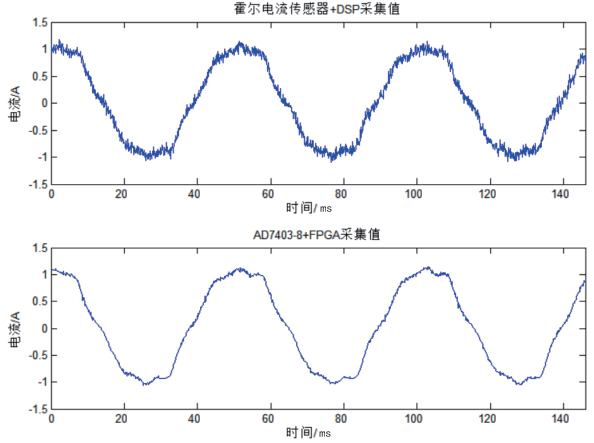

在电机输入端给定电机固定电压,霍尔传感器经DSP 处理,AD7403-8 经FPGA 处理采样到的电机电枢电流,如图5 所示。

(a)0 A电流采样对比

(b)3.22 A电流采样对比

图5 固定电流采样对比

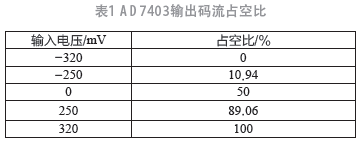

由AD7403 手册[6] 可知其输出单位码流占空比如表1 所示。

采样电阻端电压和输出码流占空比关系如式(3)所示:

![]()

其中,x 为输入电压;y 为对应的占空比;

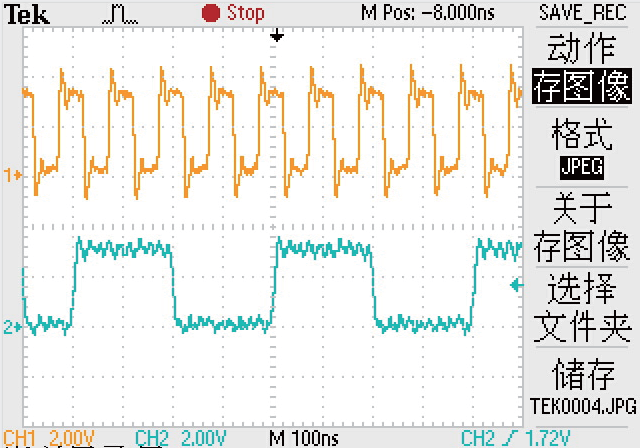

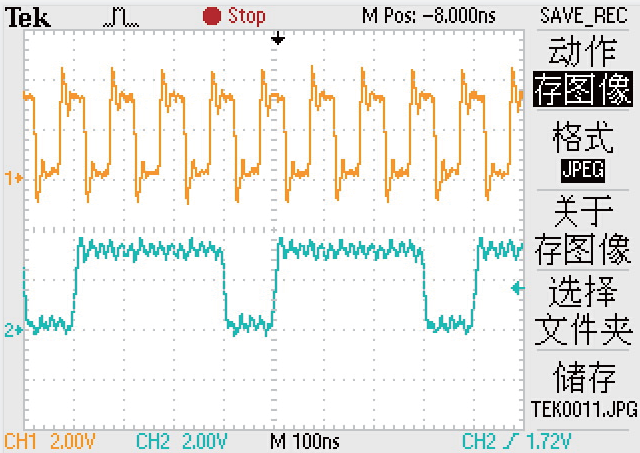

AD7403-8 输入端采样电阻为50 m Ω ,如图6 所示,AD7403-8 采样电流分别为0 A 和3.22 A,即输入端电压分别为0 mV 和161 mV,参见图6 的时钟和数据波形图。其中,通道1 为时钟波形,通道2 为数据波形。0 mV 时数据码流占空比为50%,161 mV 时数据码流占空比为75.16%,占空比符合式(3)。

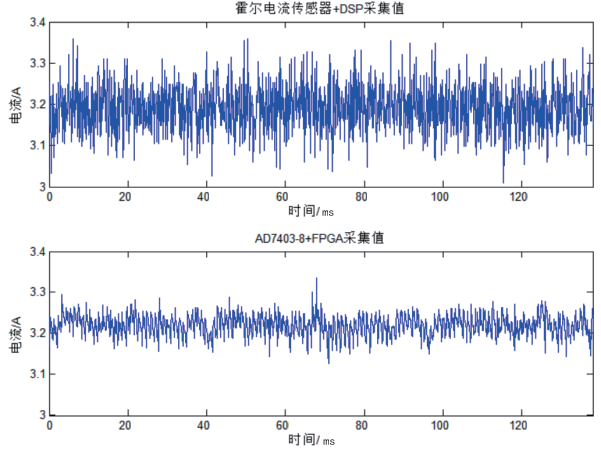

驱动电机匀速转动,霍尔传感器经DSP 采集,AD7403-8 经FPGA 处理采集到的电机电枢电流如图7所示。

(a)0 mV电压对应数据码流占空比

(b)161 mV电压对应数据码流占空比

图6 固定电压数据码流占空比

图7 霍尔电流传感器和AD7403-8动态电流采集对比

通过两种方式对上述静态和动态电流采集情况对比可见,EG4A20BG256 FPGA 和AD7403-8 配合有助于获得更高精度和更低噪声的采样结果,提升电流环的性能。

4 结论

本文利用EG4A20BG256 FPGA 设计了重构AD7403-8模数转换器的输出码流的sinc3 滤波器,根据DSP 触发实时采样重构电流值,并通过串口发送给DSP 处理,实验验证了该设计的可行性,电流采样精度较高。

参考文献:

[1] ADI公司.Σ-Δ转换用于电机控制[EB/OL]. https://www.analog.com/cn/technical-articles/sigma-delta-conversionused-for-motor-control.html.

[2] 昌鹏,高瑾.基于FPGA的永磁同步电机电流环带宽拓展的比较研究[J].电机与控制应用, 2018, 48(1):89-93.

[3] 陈小梅.适用于Sigma-Delta ADC的512倍数字抽取滤波器的设计与研究[D].武汉:华中科技大学, 2016.

[4] 安路科技公司. EAGLE FPGA 器件概览[EB/OL]. http://www.anlogic.com/down_view.aspx?TypeId=25&Id=138&Fid=t14:25:14.

[5] 杨贵杰,崔乃政,周长攀.《电机数字控制系统集成设计》系列讲座(十三)第6章 基于MCU架构交流电机数字控制系统集成设计[J]. 伺服控制, 2013, 000(005):88-94.

[6] ADI公司. AD7403中文数据手册[EB/OL]. https://www.analog.com/cn/products/ad7403.html.

(本文来源于《电子产品世界》杂志2021年5月期)

评论