- 在LTE(长期演进技术)手机基带市场取得了巨大成功后,Tensilica今日宣布,推出最新的ConnX BBE32UE DSP(数字信号处理器)IP核,用于基带SoC(片上系统)的设计。该款产品将技术过渡到LTE-Advanced,并已获得了重要客户。ConnX BBE32UE DSP IP核与Tensilica的基带数据处理器(DPU)结合,能够为支持CAT 7的LTE-Advanced终端设备提供一个完全可编程的、灵活的调制解调器,在28 nm HPL制程下功耗低于200 mW,而且能够支持2G、3G

- 关键字:

Tensilica DSP SoC

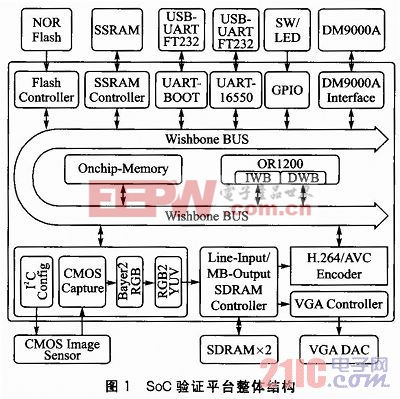

- 摘要:构建了面向H.264视频编码器的SoC验证平台,采用FPGA原型系统完成H.264编码器验证。采用Wishbone总线连接32位微处理器OR120 0以及其他的必要IP核构建基本SoC平台,并在此基础上集成H.264硬件编码模块;根据H

- 关键字:

验证 平台 SoC 编码器 视频 面向

- 论述了一种运行在FPGA芯片上应用于B超的全数字波束形成技术。采用孔径变迹、幅度加权变迹和动态变迹相结合的综合变迹技术和动态聚焦技术,两种技术均形成直观的数学模型,在FPGA上的实现方法类似,先将数学模型数字化,然后计算出数据表存入ROM,运行时将ROM中提取的数据与输入数据进行运算,即可得到预期的输出数据。在Matlab仿真和样机测试中达到了很好的抑制旁瓣和动态聚焦效果,提高了波束形成的精度。

- 关键字:

FPGA 数字波束 201202

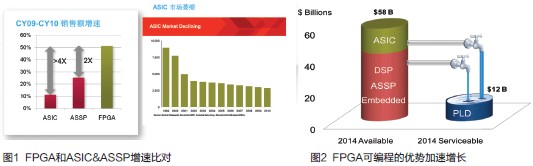

- 2011 年 12 月 13 日,可编程平台厂商赛灵思公司 (Xilinx )进驻北京新址,并开设研发中心。会上,Xilinx介绍了FPGA的发展方向

- 关键字:

Xilinx FPGA 201202

- 引 言多媒体技术实用化的关键技术之一,就是解决视频、音频数字化以后数据量大,与数字存储媒体、通信网容量小的矛盾,其解决途径就是压缩。为了支持低比特率视频传输业务,MPEG(Moving Picture Expert5 Group)推出了

- 关键字:

NiosII FPGA MPEG 视频播放器

- 1引言随着电子技术的发展,当前数字系统的设计正朝着速度快、容量大、体积小、重量轻的方向发展。推动该潮流迅猛发展的引擎就是日趋进步和完善的高密度现场可编程逻辑器件设计技术。高密度现场可编程逻辑器件(CPLD/

- 关键字:

CPLD FPGA 单片机 被动

- 基于Actel FPGA的TFT控制器技术方案设计,在1970年,Fergason制造了第一台具有实用性的LCD,从此之后,用户产品的界面发生了巨大改变,变得更加的美观、实用,在一定场合下逐渐取代传统的数码管、LED的显示。TFT诞生于80年代末,在1995年之后被广泛的应用,现

- 关键字:

技术 方案设计 控制器 TFT Actel FPGA 基于

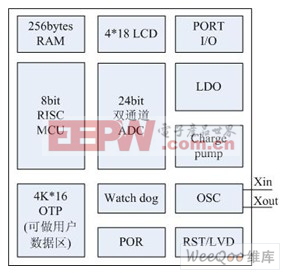

- 基于高分度、低成本、低能耗的衡器SoC方案分析与应用, 随着电子衡器产业的发展,市场对低功耗和高精度提出了越来越高的要求。深圳市芯海科技作为国内领先的模拟、数模混合集成电路设计企业,在电子衡器芯片和电能计量芯片领域具有国内领先的水平,芯海科技推出的高精度

- 关键字:

方案 分析 应用 SoC 衡器 高分 成本 能耗 基于

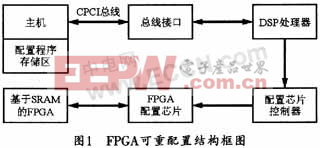

- 基于VC++的FPGA重配置方案设计,采用VC++程序的FPGA重配置设计方案利用现场可编程逻辑器件FPGA的多次可编程配置特点,通过重新下载存储于存储器的不同系统数据,从而实现不同的芯片逻辑功能,可以在很大程度上提高资源利用率。原始配置FPGA的方法是

- 关键字:

方案设计 配置 FPGA VC 基于

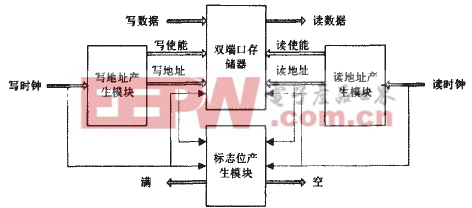

- 基于FPGA的高速异步FIFO的设计与实现,引言 现代集成电路芯片中,随着设计规模的不断扩大.一个系统中往往含有数个时钟。多时钟带来的一个问题就是,如何设计异步时钟之间的接口电路。异步FIFO(First In First Out)是解决这个问题的一种简便、快捷的解

- 关键字:

设计 实现 FIFO 异步 FPGA 高速 基于

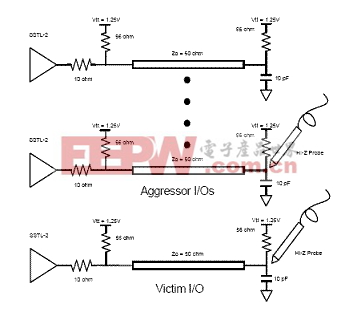

- FPGA上同步开关噪声的分析与解决方法介绍,概述 随着半导体技术的快速发展,近年来FPGA 的器件容量和输入输出的管脚数量都极大的增加了,例如StratixIV 器件,最大的一款EP4SE680 拥有68.11 万个逻辑单元和1104个输入输出管脚。大量的输出管脚在同一时刻翻

- 关键字:

解决 方法 介绍 分析 噪声 同步 开关 FPGA

- 摘要 给出了某机载实时视频图形处理系统的硬件电路设计方案,以XC5VFX70T FPGA作为核心处理器,实现了对DVI及PAL等多种格式视频信号的解码、实时处理以及输出。系统电路设计简洁,具有较强的灵活性和扩展性。文中介绍

- 关键字:

FPGA 机载 实时视频 图形处理系统

- 基于FPGA的双口RAM实现及应用,摘要:为了在高速采集时不丢失数据,在数据采集系统和CPU之间设置一个数据暂存区。介绍双口RAM的存储原理及其在数字系统中的应用。采用FPGA技术构造双口RAM,实现高速信号采集系统中的海量数据存储和时钟匹配。功能仿

- 关键字:

实现 应用 RAM 双口 FPGA 基于

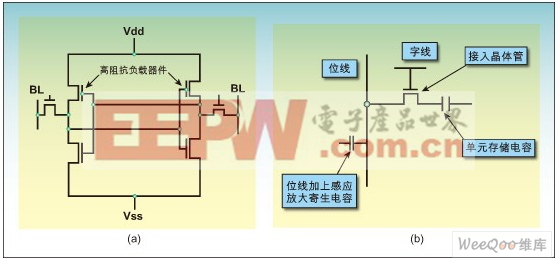

- 使用新SRAM工艺实现嵌入式ASIC和SoC的存储器设计,基于传统六晶体管(6T)存储单元的静态RAM存储器块一直是许多嵌入式设计中使用ASIC/SoC实现的开发人员所采用的利器,因为这种存储器结构非常适合主流的CMOS工艺流程,不需要增添任何额外的工艺步骤。如图1a中所示的那样

- 关键字:

SoC 存储器 设计 ASIC 嵌入式 SRAM 工艺 实现 使用

fpga soc介绍

您好,目前还没有人创建词条fpga soc!

欢迎您创建该词条,阐述对fpga soc的理解,并与今后在此搜索fpga soc的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473