- 这些功能大部分都集中在Analysis菜单下。 1. Silk to Solder Spacing 这是软件自动检验丝印层与阻焊层间距的功能。Analysis -> Silk to Solder Spacing就会弹出“Check Silkscreen”对话框。 首先

- 关键字:

CAM 350 DFM

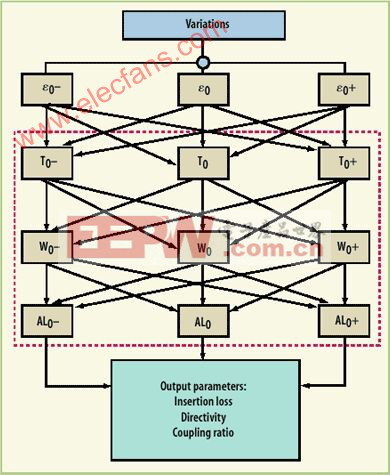

- 低温共烧陶瓷(LTCC)电路技术支持紧凑型多层设计并被广泛用于无线应用,特别是在RF模块和包内系统(SiP)设计中。相对于层压技术,它具有一系列优势,尽管其工艺与层压印刷电路板材料的处理工艺类似。其典型好处是较低的

- 关键字:

一次 设计 成功 实现 方法 LTCC DFM 利用

- 中心议题: 可制造性设计(DFM)流程 可制造性设计(DFM)工具 解决方案: 产品PCB制作 产品零部件组装 产品成品测试

“DFM”-一个由三个字母组成的缩写,其意义依据你在设计及制造流程链中所扮演的角色不同而不同

- 关键字:

PCB DFM 可制造性 设计分析

- 时间: 2010年3月17日

地点: 上海东锦江索菲特大酒店

IPC设计师理事会中国分会将于2010年3月17日举办2010年度首次PCB设计师活动日。此次活动日将邀请二位理事会的国内专家及一位IPC总部的PCB设计专家做有关PCB设计的专题演讲。

三位专家将在设计师活动日做精彩演讲,与理事会成员共享交流他们在PCB设计领域的经验。

诚邀您的光临!

1. 日程安排

IPC设计师理事会中国分会2010年首次PCB设计师活动日日程安排

- 关键字:

PCB DFM CAD

- 现在,重新可编程成为产品设计团队所必备的能力,他们充分利用这一能力尽快将产品推向市场,尽量延长产品在市时间。FPGA的功能、容量、性能在不断提高,而功耗和成本显著下降,足以成为大批量、低成本应用非常可靠的选择方案之一。

对于采用了单芯片方案且面向全球市场的新产品,应能为不同区域市场提供各种各样特性的产品。从工业、消费类到军事

- 关键字:

重新可编程 FPGA DFM Altera

- Cadence设计系统公司宣布其多种领先技术已经纳入TSMC参考流程9.0版本中。这些可靠的能力帮助设计师使其产品更快地投入量产,提供了自动化的、前端到后端的流程,实现高良品率、省电型设计,面向晶圆厂的40纳米生产工艺。

Cadence已经在多代的工艺技术中与TSMC合作,开发参考流程,提供低功耗设计能力和高级DFM方法学。通过参考流程9.0,Cadence将这些性能拓展到该晶圆厂的40纳米工艺节点,使用光刻物理分析和强化的统计静态时序分析能力,此外一直追随TSMC参考流程的Cadence已经支

- 关键字:

Cadence 晶圆 设计 DFM 低功耗

- 全球电子设计创新企业Cadence设计系统公司(NASDAQ: CDNS)今天宣布其多种领先技术已经纳入TSMC参考流程9.0版本中。这些可靠的能力帮助设计师使其产品更快地投入量产,提供了自动化的、前端到后端的流程,实现高良品率、省电型设计,面向晶圆厂的40纳米生产工艺。

“TSMC和Cadence之间的合作提供了自动化的设计技术,这是在高级工艺节点上实现低风险和快速量产的必要技术,”TSMC设计基础架构营销部高级主管S.T. Juang说。

Cadence已经在多

- 关键字:

Cadence TSMC DFM

- IC芯片产业在进入纳米时代后,生产工艺复杂度和物理极限等局限开始挑战被称为定律的“Moor’s Law”。同时,EDA技术的发展不但完全融入到电子产品的设计和定型过程中,并且开始涉足包括存档、生产、制造、测试等环节,帮助IC产业迎接工艺极限的挑战。

作为EDA行业的佼佼者,Mentor Graphics公司一年一度的“Mentor Graphics EDA Tech Forum 2007”备受关注。今年的技术论坛以 “洞悉您最复杂的设计挑战!”为主题在全球18个城市巡回开展。8月31日,Ment

- 关键字:

嵌入式系统 单片机 0710_A 杂志_业界风云 DFM MCU和嵌入式微处理器

- 有鉴于半导体产业正试图解决可制造性设计(DFM)问题,参与月前在美国举行之SemiconWest展会上的一场小组座谈的EDA产业专家表示,可以从可测试性设计(design-for-test,DFT)的技术发展历程中取经。 该场小组座谈会的主持人、市场研究公司GarySmithEDA总裁GarySmith表示:「真正的DFM是个大问号,如果它跟随DFT的脚步,得花上几年时间才能在设计社群中扎根。」他指出,半导体公司基本上是把DFT强迫推销给设计工程师

- 关键字:

嵌入式系统 单片机 纳米 IC DFM 嵌入式

- CADENCE发布了Cadence Encounter 数字IC设计平台的最新软件版本,增加了业内领先的功能特性,包括全芯片优化、面向65纳米及以下工艺的超大规模混合信号设计支持,具有对角布线能力的Encounter X Interconnect Option,以及之前已经公布支持的基于Si2通用功率格式(CPF)1.0版本的低功耗设计。新平台提供了L、XL和GXL三种配置,为先进半导体设计提供更佳的易用性,更短的设计时间以及更高的性能。 “最新版本Enc

- 关键字:

CADENCE DFM ENCOUNTER 电源技术 模拟技术 EDA IC设计

- 解决45纳米及以下工艺相关变异问题 创新的工艺识别DFM系列产品有助于设计者减少工艺变异的影响, 改善先进半导体的制造设计 全球领先的电子设计自动化(EDA)软件工具领导厂商Synopsys推出了具备工艺识别功能的可制造性设计(DFM)新系列产品PA-DFM,用于分析45纳米及以下工艺定制/模拟设计阶段的工艺变异的影响。随着工艺尺寸的日益减小,先进硅技术将引起更多如应力工程的变异问题,这将越来越影响电路的性能。Synopsys PA-DFM系列的核心产品Seismos 和 P

- 关键字:

DFM Synopsys 通讯 网络 无线

dfm介绍

DFM(Design for Manufacture)是指可制造设计,过去在芯片设计流程中,IC设计业者将电路设计交由晶圆代工厂生产的垂直分工,在进入先进制程技术时遇到了困难,原因是制程技术愈来愈复杂,设计与生产之间的整合沟通必须更加紧密,因此,IC制造业者必须有套完整的DFM,让IC设计业者得以用其中的设计流程等规范早期便融入设计IC阶段中,以提升芯片的设计、生产效率。因此,从制造者的观点, [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473