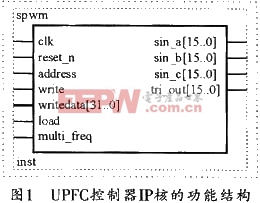

- 0 引言 统一潮流控制器(Unified Power Flow Con-troller,简称UPFC)是一种可以较大范围地控制电流使之按指定路经流动的设备,它可在保证输电线输送容量接近热稳定极限的同时又不至于过负荷。控制系统是UPFC的核

- 关键字:

IP 设计 控制器 UPFC FPGA 基于

- ASIC与ARM的“强手联合”,引言嵌入式世界的范围和概念极其广泛,可以从ASIC到MCU,而ASIC是有着巨大的潜力和创新力的一种技术,尽管它的设计非常昂贵,并且所需世界要花费数年,但这依然不影响它的巨大市场潜力。相比而言,单片机方案就便宜得

- 关键字:

联合 强手 ARM ASIC

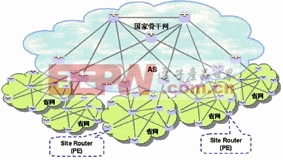

- 毋庸置疑,现代通信网络的发展,是由业务需求和市场需求来决定的,而不是技术的发展。我们回头看看互联网(IP网络)的发展历程,这其中市场推动的痕迹非常明显:这一种六七十年代就已经诞生的IP网络技术,在九十年代

- 关键字:

探讨 规划设计 网络 承载 IP

- 摘要 为降低FPGA实现3电平SVPWM算法的复杂性,减小SVPWM模块所占用的资源,文中利用正弦函数和余弦函数的关系,采用小容量ROM提出了一种新的SVPWM控制算法。利用Verilog HDL实现了算法的硬件设计,并封装成IP核以方便

- 关键字:

SVPWM Nios Core IP

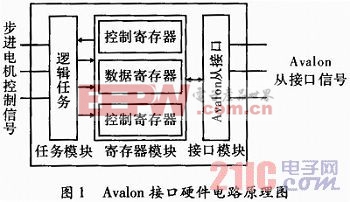

- 摘要 根据Nios II处理器的Avalon总线规范,设计了一款面向步进电机的控制器IP核。该定制IP核采用软、硬件协同设计的方法,功能符合Avalon总线的读写传输时序,具有完备的步进电机驱动能力。仿真结果表明,该IP核具有

- 关键字:

IP 设计 实现 控制器 电机 Nios II 步进 基于

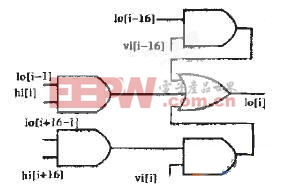

- 摘要:星载计算机系统处于空间辐照环境中,可能会受到单粒子翻转的影响而出错,三模冗余就是一种对单粒子翻转有效的容错技术。通过对三模冗余加固电路特点的分析,提出了在ASIC设计中实现三模冗余的2种方法。其一是通

- 关键字:

方法 实现 设计 ASIC 余在

- 毋庸置疑,现代通信网络的发展,是由业务需求和市场需求来决定的,而不是技术的发展。我们回头看看互联网(IP网络)的发展历程,这其中市场推动的痕迹非常明显:这一种六七十年代就已经诞生的IP网络技术,在九十年代

- 关键字:

分析 规划设计 网络 承载 IP

- ATM可以提供空前的可伸缩性和性价比,以及对将来的实时业务、多媒体业务等的支持,ATM将扮演重要的角色。但目前的信息体系,即LAN和WAN,建立在网络层协议如IP、IPX、AppleTalk等的基础上,因此,ATM的成功及Internet

- 关键字:

技术 介绍 兼容 IP 网络 ATM

- 基于IP复用和SOC技术的微处理器FSPLCSOC模块设计,1 引言 文中采用IP核复用方法和SOC技术基于AVR 8位微处理器AT90S1200IP Core设计专用PLC微处理器FSPLCSOC模块。随着芯片集成程度的飞速提高,IC产业中形成了以片上系统SOC(System-on-Chip)技术为主的设计方式。一

- 关键字:

FSPLCSOC 模块 设计 微处理器 技术 IP 复用 SOC 基于

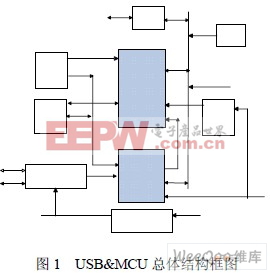

- MCUUSB设备控制器IP核的设计,摘要:用硬件描述语言verilog HDL设计实现了一种MCUUSB设备控制器IP核。论文首先简要介绍了设计的背景,重点对自主研发的将MCUUSB控制器集成于一个芯片的设计和研究分析。最后给出nc-verilog功能仿真方案以及FPGA验

- 关键字:

设计 IP 控制器 设备 MCU&USB

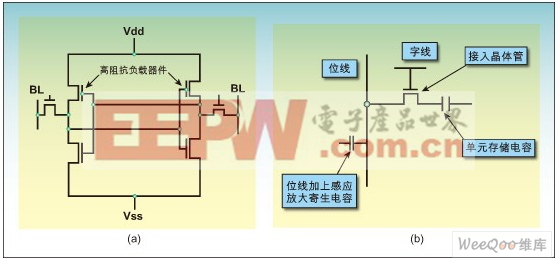

- 使用新SRAM工艺实现嵌入式ASIC和SoC的存储器设计,基于传统六晶体管(6T)存储单元的静态RAM存储器块一直是许多嵌入式设计中使用ASIC/SoC实现的开发人员所采用的利器,因为这种存储器结构非常适合主流的CMOS工艺流程,不需要增添任何额外的工艺步骤。如图1a中所示的那样

- 关键字:

SoC 存储器 设计 ASIC 嵌入式 SRAM 工艺 实现 使用

- FPGA入门知识,什么是FPGA?FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、EPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路

- 关键字:

fpga ASIC 什么意思

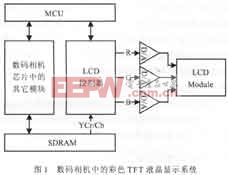

- 摘要:介绍了一种用于高级型数码相机的彩色TFT液晶显示控制电路的设计。文中首先简单给出了控制电路的设计要求,然后重点介绍电路中各模块的设计以及FPGA验证。整个电路作为数码相机专用集成电路芯片的一部分采用TSM

- 关键字:

ASIC 实现 电路设计 控制 TFT 液晶显示 彩色

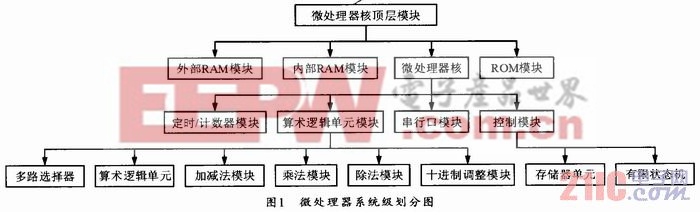

- 嵌入式微处理器IP core设计与分析,摘要:本文在对传统微控制器进行系统分析的基础上,提出了一种较好的改进设计方法。回避了传统微控制器基于累加器的ALU结构及算术逻辑指令:并在指令执行时序上尽量减少指令执行所需的时钟周期。通过仿真验证证明该设

- 关键字:

设计 分析 core IP 微处理器 嵌入式

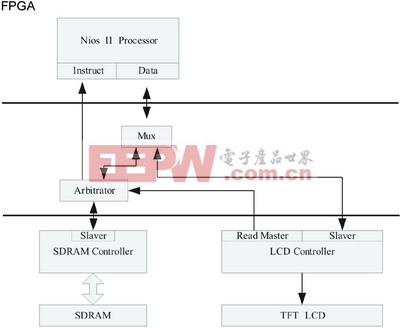

- 系统总体设计方案本系统的总体设计框图如图1所示。

图1 系统框图

Nios II处理器在SDRAM中开辟帧缓冲(Frame buffer),可以是单缓冲也可以是双缓冲。以单缓冲为例。处理器将一帧图像数据(640times;480times;2Byt

- 关键字:

IP 驱动 设计 LCD TFT 嵌入式 Linux 基于

asic ip介绍

您好,目前还没有人创建词条asic ip!

欢迎您创建该词条,阐述对asic ip的理解,并与今后在此搜索asic ip的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473