- 1 概述 JPEG2000[1,2]是新的静止图像压缩标准,它具有的多种特性使得它有着广泛的应用前景。目前为止,JPEG2000的解决方案比较少,并且其中的绝大部分是软件解决方案:Jasper[3]软件是经IEC JTC1/SC29/WG1小组推荐

- 关键字:

IP 设计 编码器 算术 Q-Coder 基于

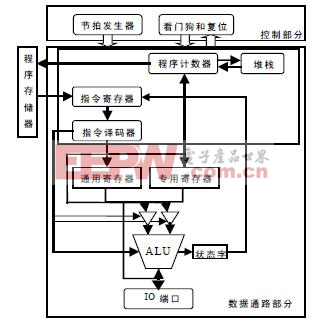

- 8位RISC MCU IP软核仿真的新方法, 本文提出的建立虚拟指令存储器模块对MCU IP核仿真的方案和自动生成指令测试文件的方法,大大提高了MCU IP核仿真和验证的效率。此方法不仅对本文中MCU IP核的仿真和验证有效,也可用于同类中其它IP核的仿真和验证。例如当对MCU进行升级设计、扩展寻址范围或指令宽度时,只要修改仿真文件和转化程序的相关参数即可。

- 关键字:

真的 方法 软核 IP RISC MCU 8位

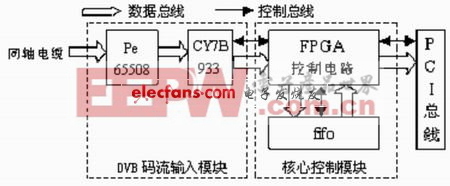

- PCI接口IP核的DVB码流接收系统设计,随着数字化广播电视技术的迅速发展和基于MPEG-2标准的图像压缩和复用技术的完善,利用PC对大容量信息的处理变得日益重要,如基于PC的软复用器的实现,使得通过PC接收DVB(数字视频广播)码流已逐渐成为一项不可替代的多

- 关键字:

系统 设计 接收 DVB 接口 IP PCI

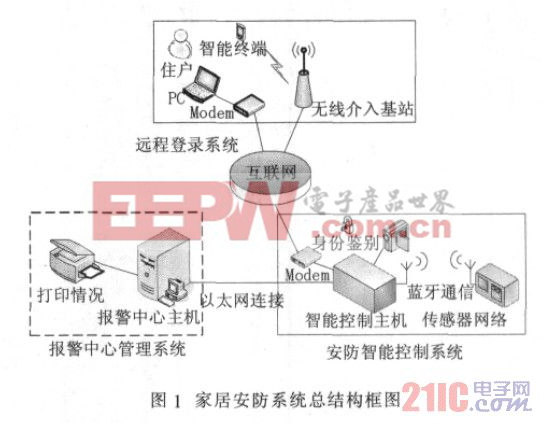

- 引言 目前,国内外现有的数字家居安防系统的架构主要基于传统的有线网络技术,普遍存在着布线烦琐,无法实现移动访问、施工周期长、后期维护困难、可扩展性差等问题,限制了它在数字家居系统中的应用。 针

- 关键字:

TCP/IP 桥梁 通信 安防 家居

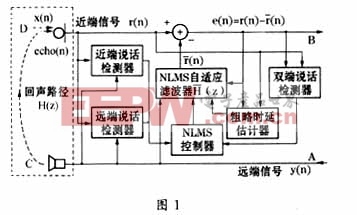

- IP电话回声消除器的设计及其DSP实现,介绍了一种用于IP电话中的自适应回声消除器,采用归一化最小二乘(NLMS)自适应滤波器实现,包括语音模式检测器和粗略时延估计器。最后以TI公司的TMS320C5402 DSP芯片为平台,实现了该回声消除器,还对关键代码进行了

- 关键字:

及其 DSP 实现 设计 消除器 电话 回声 IP

- 一种ASIC硬件图像匹配最大互相关算法的设计和实现,图像匹配是指通过一定的匹配算法在两幅或多幅图像之间识别同名点,如二维图像匹配中通过比较目标区和搜索区中相同大小的窗口的相关系数,取搜索区中相关系数最大所对应的窗口中心点作为同名点。其实质是在基元相似性

- 关键字:

相关 算法 设计 实现 最大 匹配 ASIC 硬件 图像 一种

- 参数化可配置IP核浮点运算器的设计与实现,将参数化可配置IP核的设计方法引入到浮点运算器设计中,通过设计时提取的可用参数,将浮点运算器设计成为参数化、可配置、可重用的IP核。通过仿真验证了实现参数化IP核浮点运算器的可行性和有效性。

- 关键字:

设计 实现 运算 浮点 配置 IP 参数

- include timescale.v// synopsys translate_on`include can_defines.v module can_top( `ifdef CAN_WISHBONE_IF wb_clk_i, wb_rst_i, wb_dat_i, wb_dat_o, wb_cyc_i, wb_stb_i, wb_we_i,

- 关键字:

代码 分析 IP 控制器 总线 CAN

- 一、全面认识高清1.1高清不仅仅是高清IP,还有数字高清、模拟高清。高清IP从感光器件上又可分为...

- 关键字:

高清 IP

- 工业和信息化部等七部门发布了关于推进光纤宽带网络建设的意见>>,计划到2011年光纤宽带端口达到8000万个,城市用户的接入能力平均达到8Mbit/s以上,农村用户的接入能力平均达到2Mbit/s以上,商业楼宇用户基本达到

- 关键字:

骨干网 转型 传输 和光 IP 融合

- 恩智浦半导体NXP Semiconductors N.V. (NASDAQ:NXPI) 今日宣布将以开源授权方式提供其JenNet-IP超低功耗IEEE 802.15.4无线连接网络层软件,作为其“物联网”实施计划的一部分。近年来,人们对物联网的兴趣与日俱增,在物联网中,每台设备都有一个IP地址,可以通过安全互联网连接进行监视和控制。然而,物联网普及所面临的主要障碍是不同应用都有不同的网络软件。通过发布基于开源授权的JenNet-IP网络层软件,并为众多开发者和用户提供支持,恩智浦志在简化为多种设备添加“

- 关键字:

恩智浦 JenNet-IP

- 基于OCP-IP的SOC总线即插即用的实现,本文讨论了OCP-IP的协议与特点,设计了基于AMBA总线的OCP-IP接口,提出了一种IP自动封装的方法,为IP核的集成和管理带来极大的方便。

- 关键字:

实现 总线 SOC OCP-IP 基于

- 由于移动智能终端的成熟、HSPA的规模商用和无线数据业务资费的下降,移动对固定业务的替代也从语音蔓延到...

- 关键字:

LTE 移动宽带 IP RAN 智能终端

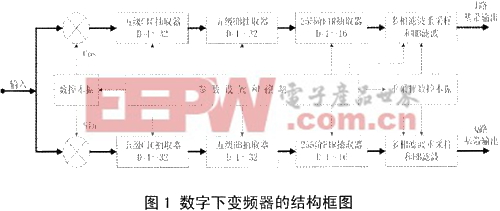

- 数字下变频(DDC)中坐标变换模块的ASIC实现,数字下变频器中坐标变换模块的ASIC实现1.引言

数字下变频(DDC)技术是软件无线电接收机的核心技术。其基本功能是从输人的宽带高速数字信号中提取所需的窄带信号,将其下变频为数字基带信号,并转换成较低的数据率

- 关键字:

模块 ASIC 实现 变换 坐标 变频 DDC 数字

asic ip介绍

您好,目前还没有人创建词条asic ip!

欢迎您创建该词条,阐述对asic ip的理解,并与今后在此搜索asic ip的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473