2014年2月20日,全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS)宣布已收购美商传威(TranSwitchCorp.)公司高速接口IP资产,并雇用其经验丰富的IP开发团队,更进一步扩大Cadence快速发展的IP产品阵容。

关键字:

Cadence 美商传威 IP

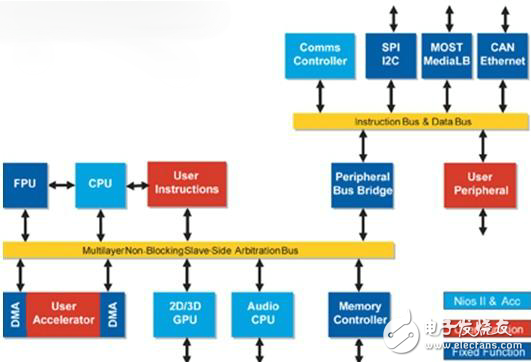

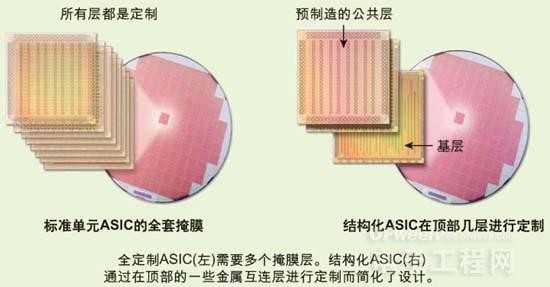

摘要:本文提出了一种基于低成本FPGA的高清低码流安防摄像机SoC实现方式,该设计已经完全实现,开创了高清低码流安防摄像机SoC的先河。

关键字:

FPGA SoC ASIC 摄像机 传感器

在汽车电子中广为采用的微控制器(MCU)正快速面临时间和成本的压力。使用MCU的主要优势一直以来都是‘创造具有高性价比的高阶系统整合’。然而,在此一优势之下,有一些与元件本身相关的潜在成本是超乎于其单价水平的。例如,若选用的元件无法创造所需特性,则必须增加外部逻辑、软件或其它整合元件。

关键字:

微控制器 FPGA ASIC CPU 嵌入式

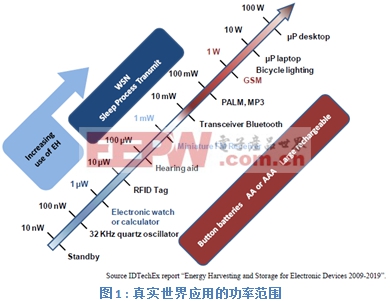

近年来,能量收集(energy harvesting)话题在电子设计群体内获得了广泛关注。通过能量收集过程,能够捕获、收集然后透过电子设备来利用小批量的能量,从而能够完成简单的任务,而无须在系统设计中集成传统电源。

关键字:

安森美 能量收集 OEM 太阳能 ASIC

电子产品世界,为电子工程师提供全面的电子产品信息和行业解决方案,是电子工程师的技术中心和交流中心,是电子产品的市场中心,EEPW 20年的品牌历史,是电子工程师的网络家园

关键字:

传感器 ASIC MEMS 协同设计

IP在电子行业,让人又爱又恨,既可以让人富得流油,也可以让人瞬间两手空空。为保行业可持续发展,我国政府越来越重视IP问题,本土IP业面临着诸多困惑和选择,“弱者愈弱,强者恒强”,IP公司将来命运如何?

关键字:

半导体 IP

中国人行不承认比特币(Bitcoin)为交易货币,但比特币在PayPal等网站上仍可使用,全球仍有许多「矿工」投入挖矿行列。由于专业「挖矿机」需要强大的平行运算功能来进行比特币挖矿,高阶绘图晶片及专用特殊应用晶片(ASIC)需求强劲,台积电(2330)受惠最大。

比特币的发行不需透过第三方单位,而是由蕴藏比特币的矿山,每10分钟主动产生一个区块,只要完成区块内数据运算,就可获得比特币。由于比特币每4年的每一区域产量将减少一半,现在每区域只能生产25个比特币,所以参与运算的「矿工」,就得利用专业「

关键字:

台积电 ASIC

在OTN帧结构中,Serdes在从高速的串行数据中恢复出数据后,数据只是按顺序以64bit为宽度重新放置,并没有按字节对齐,所以后续电路无法直接使用这样的数据。需要帧头定位电路找到帧头后,把所有的数据按字节对齐。但是将OTN数据转换为并行的数据后,存在着数据速率高,位宽大的问题。在ASIC或FPGA中,大量的大位宽的数据,是不容易运行在较高的速率下的。所以需要对帧定位电路进行简化,以使得电路在大位宽时,仍然能够进行高速运行。研究了OTN数据的帧结构后,提出了一种适合于高速率的、大位宽的处理电路。

关键字:

OTN FPGA Serdes ASIC 帧定位 201401

“在SoC中增加USB 3.0功能,若芯片设计公司做得好,与其他人没差别;做得不好,和人家差别很大。”新思科技(Synopsys)公司总裁兼联合CEO陈志宽博士说。“现在很多芯片需要IP设计,因为芯片太复杂了,芯片里有很多block(功能部分)。”

关键字:

SoC USB 新思 IP

对于芯片设计师,20年前做逻辑综合,写软件时,A+B就可以了。现在IP在芯片中的比例提高了,有时40%或60%是IP,这种方法就不行了。也许我们都懂得USB、DDR、ARM的关系是怎么样,可能你理解得比我好,所以你做出来的芯片性能也比较高。

关键字:

IP ARM USB

各种 IP Core和参考设计以下各种 IP Core和参考设计是由相关设计者提供,可以免费下载学习或使用。[使用注 ...

关键字:

IP Core 参考设计

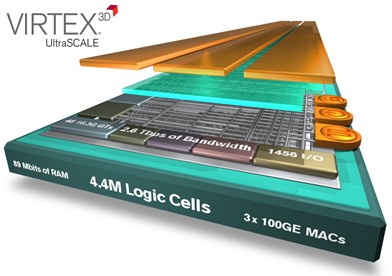

赛灵思宣布推出20nm All Programmable UltraScale™产品系列,并配套提供产品技术文档和Vivado®设计套件支持。继2013年11月首款20nm芯片发货后,赛灵思继续积极推动UltraScale器件系列发货进程。该器件系列采用业界唯一的ASIC级可编程架构以及Vivado ASIC增强型设计套件和UltraFast™设计方法,提供了可媲美ASIC级的性能优势。

关键字:

赛灵思 UltraScale ASIC 以太网

All Programmable FPGA、SoC和3D IC的全球领先企业赛灵思公司 (Xilinx, Inc. (NASDAQ:XLNX) )日前发布拥有440万个逻辑单元的创纪录产品,其密度是业界最高密度产品Virtex® -7 2000T的两倍以上,该器件使其成功在高端器件市场连续两代保持领先优势,并为客户提供了超越工艺节点的价值优势。

关键字:

赛灵思 Virtex ASIC SSI

电子产品世界,为电子工程师提供全面的电子产品信息和行业解决方案,是电子工程师的技术中心和交流中心,是电子产品的市场中心,EEPW 20年的品牌历史,是电子工程师的网络家园

关键字:

IP 安全性 嵌入式系统

asic ip介绍

您好,目前还没有人创建词条asic ip!

欢迎您创建该词条,阐述对asic ip的理解,并与今后在此搜索asic ip的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473