- 楷登电子(美国Cadence 公司)今日宣布,业界首款支持全新 PCI Express ® (PCIe®)5.0 架构的验证 IP(VIP)正式可用。结合 TripleCheck™ 技术,Cadence® VIP 旨在帮助设计师快速执行基于 PCIe 5.0 标准的服务器和存储器的系统级芯片(SoC)设计的完整功能性验证,确保产品功能符合设计初衷。 如需进一步了

- 关键字:

Cadence IP

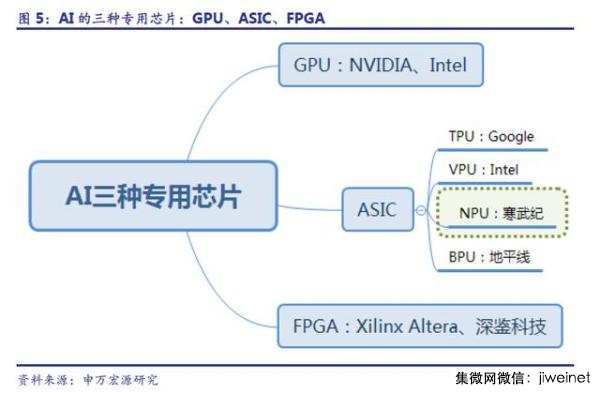

- 人工智能系统开发近年快速跃进,战场已从过去「软件开发」走向「硬件芯片」竞争,搭配网络普及型塑出大数据,使得真实世界的无限复杂与快速计算可以藉由AI实现。

- 关键字:

AI ASIC

- 在“中国集成电路设计业2017年会”(ICCAD会议)上,部分EDA工具供应商、芯片代工厂、IP公司等预测了本土IC公司2018年的热门应用,并分析了本土芯片设计公司的特点。

- 关键字:

IC设计 IP 系统 本土 201712

- 人工智能相关ASIC近来渐获市场注意,多家厂商如NVIDIA、英特尔、Google及部分新创企业均相继抢进开发,有望在未来形成数十亿美元市场商机规模。

- 关键字:

ASIC 人工智能

- AI芯片不会是一两颗芯片打遍天下,而一定是针对不同的应用类型处理,由不同的芯片来支持,是很多款芯片的融合。FPGA、GPU、ASIC三大主要AI芯片将在很长一段时间内同时存在。

- 关键字:

ASIC FPGA

- 根据Semico Research,在未来几年,人工智能将以图形辨识、语音辨识和语言翻译等各种形式,出现在几乎每一款装置与应用中…

根据Semico Research的最新调查报告,在2021年以前,人工智能(AI)声控装置ASIC的设计预计将以接近20%的复合年成长率(CAGR)成长,几乎达到2016年至2021年间所有ASIC设计成长率(10.1%)的两倍。

随着Amazon Echo和Google Home等声控数位助理的普及,加上普遍对于人工智能(AI)进行设计的狂热

- 关键字:

人工智能 ASIC

- 联发科共同CEO蔡力行表示,对于明年营运预估乐观成长,联发科也持续朝向多面向布局,包括5G、AI、车用电子等领域, 至于被问及ASIC的布局,他则说会发挥联发科既有资源,但毕竟才刚开始,「联发科现阶段当然不会太挑客户」,还是以整体业务成长为优先考虑。

蔡力行表示,联发科对于5G持续也持续努力,相关芯片产品也都会跟上5G的发展,为2020年的商转作准备,联发科对5G得规划是很完整的,至于被问及是否会想在高通前发表5G芯片产品,他幽默响应,「可能要先去问问他们(高通)」, 针对今日传出苹果有可能排除

- 关键字:

联发科 ASIC

- 想一次性流片成功 ASIC设计中这些问题不可忽视-ASIC的复杂性不断提高,同时工艺在不断地改进,如何在较短的时间内开发一个稳定的可重用的ASIC芯片的设计,并且一次性流片成功,这需要一个成熟的ASIC的设计方法和开发流程。

- 关键字:

asic

- 将数据转换器IP集成到系统芯片简化设计技术-为了实现数据转换器IP性能最大化,系统芯片设计师必须应对将数据转换器与系统芯片集成的挑战,避免危害整个系统性能的缺陷。本文系统地介绍了12种简化设计技术,这些技术解决了系统集成中的所有常见问题,有助确保在系统芯片中成功集成高性能数据转换器。

- 关键字:

电源 IP 数据转换器 Synopsys

- ASIC、ASSP、SoC和FPGA之间到底有何区别?-我经常收到关于各类设备之间的差异的问题,诸如ASIC、ASSP、SoC和FPGA之间的区别问题。例如是SoC是ASIC吗?或ASIC是SoC吗?ASIC和ASSP之间的区别是什么?以及高端FPGA应该归类为SoC吗?

- 关键字:

FPGA SoC ASSP ASIC

- 五大优势凸显 可编程逻辑或将呈现快速增长-可编程逻辑器件的两种类型是现场可编程门阵列(FPGA)和复杂可编程逻辑器件(CPLD)。在这两类可编程逻辑器件中,FPGA是在PAL、GAL、EPLD等可编程器件的基础上进一步发展的产物。

- 关键字:

ASIC FPGA CPLD 半导体芯片

- 根据新的研究报告“IP设计IP(IP处理器IP,接口IP,内存IP)”显示,半导体知识产权市场预计到2023年将达到6.22万亿美元,2017 - 2023年之间的复合年增长率为4.87% 。驱动这个市场的主要因素包括消费电子行业的多核技术的进步,以及对现代SoC设计的需求增加,导致市场增长,以及对连接设备的需求也不断增长。

消费电子在预测期间占据半导体IP市场的最大份额

各地区消费电子产品的使用量的增加正在推动消费电子行业半导体IP市场的增长。此外,APAC和Ro

- 关键字:

IP SoC

- 谈谈如何利用FPGA开发板进行ASIC原型开发-ASIC设计在尺寸和复杂性上不断增加,现代FPGA的容量和性能的新进展意味着这些设计中的2/3能够使用单个FPGA进行建模。

- 关键字:

FPGA ASIC

- 如何在EDK中使用自己的 IP核?-如何在EDK中使用自己的 IP核呢? 这是很多人梦寐以求的事情。然而在EDK以及ISE的各种文档中对此却遮遮掩掩,欲语还休。

- 关键字:

赛灵思 ISE IP

- 用CORDIC IP产生SINE波形-以ISE10.1软件为例,其集成的CORDIC算法IP为V3.0版本,具体步骤如下:

- 关键字:

CORDIC IP SINE

asic ip介绍

您好,目前还没有人创建词条asic ip!

欢迎您创建该词条,阐述对asic ip的理解,并与今后在此搜索asic ip的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473