- 根据Semico Research,在未来几年,人工智能将以图形辨识、语音辨识和语言翻译等各种形式,出现在几乎每一款装置与应用中…

根据Semico Research的最新调查报告,在2021年以前,人工智能(AI)声控装置ASIC的设计预计将以接近20%的复合年成长率(CAGR)成长,几乎达到2016年至2021年间所有ASIC设计成长率(10.1%)的两倍。

随着Amazon Echo和Google Home等声控数位助理的普及,加上普遍对于人工智能(AI)进行设计的狂热

- 关键字:

人工智能 ASIC

- 联发科共同CEO蔡力行表示,对于明年营运预估乐观成长,联发科也持续朝向多面向布局,包括5G、AI、车用电子等领域, 至于被问及ASIC的布局,他则说会发挥联发科既有资源,但毕竟才刚开始,「联发科现阶段当然不会太挑客户」,还是以整体业务成长为优先考虑。

蔡力行表示,联发科对于5G持续也持续努力,相关芯片产品也都会跟上5G的发展,为2020年的商转作准备,联发科对5G得规划是很完整的,至于被问及是否会想在高通前发表5G芯片产品,他幽默响应,「可能要先去问问他们(高通)」, 针对今日传出苹果有可能排除

- 关键字:

联发科 ASIC

- 想一次性流片成功 ASIC设计中这些问题不可忽视-ASIC的复杂性不断提高,同时工艺在不断地改进,如何在较短的时间内开发一个稳定的可重用的ASIC芯片的设计,并且一次性流片成功,这需要一个成熟的ASIC的设计方法和开发流程。

- 关键字:

asic

- 一种新型的LCD驱动电路IP核的总体设计-本文介绍了LCD的通用驱动电路IP核设计,采用自顶向下的设计方法将其划分为几个主要模块,分别介绍各个模块的功能,用VHDL语言对其进行描述,用FPGA实现并通过了仿真验证。该IP核具有良好的移植性,可驱动不同规模的LCD电路。

- 关键字:

IP核 驱动电路 LCD

- GPIB控制器软件的IP核设计方案详解-随着网络技术与通信技术的高速发展,测试仪器和测试技术发生了革命性变化,“网络就是仪器”确切地概括了测试仪器间的网络化发展趋势。

- 关键字:

IP核 GPIB

- ASIC、ASSP、SoC和FPGA之间到底有何区别?-我经常收到关于各类设备之间的差异的问题,诸如ASIC、ASSP、SoC和FPGA之间的区别问题。例如是SoC是ASIC吗?或ASIC是SoC吗?ASIC和ASSP之间的区别是什么?以及高端FPGA应该归类为SoC吗?

- 关键字:

FPGA SoC ASSP ASIC

- 五大优势凸显 可编程逻辑或将呈现快速增长-可编程逻辑器件的两种类型是现场可编程门阵列(FPGA)和复杂可编程逻辑器件(CPLD)。在这两类可编程逻辑器件中,FPGA是在PAL、GAL、EPLD等可编程器件的基础上进一步发展的产物。

- 关键字:

ASIC FPGA CPLD 半导体芯片

- 谈谈如何利用FPGA开发板进行ASIC原型开发-ASIC设计在尺寸和复杂性上不断增加,现代FPGA的容量和性能的新进展意味着这些设计中的2/3能够使用单个FPGA进行建模。

- 关键字:

FPGA ASIC

- FPGA实战开发技巧(13)-基于IP的设计已成为目前FPGA设计的主流方法之一,本章首先给出IP的定义,然后以FFT IP核为例,介绍赛灵思IP核的应用。

- 关键字:

FPGA 赛灵思 IP核

- 什么是FPGA,ASIC,如何设计一个适用于它们的供电系统-目前,在集成电路界ASIC被认为是一种为专门目的而设计的集成电路。是指应特定用户要求和特定电子系统的需要而设计、制造的集成电路。ASIC的特点是面向特定用户的需求,ASIC在批量生产时与通用集成电路相比具有体积更小、功耗更低、可靠性提高、性能提高、保密性增强、成本降低等优点

- 关键字:

fpga asic 电源

- 作为可配置标准单元ASIC解决方案佼佼者,BaySand, Inc.(倍赛达)宣布:公司现在可提供采用Arm® Cortex®-M0和Cortex-M3处理器定制系统级芯片(SoC)的设计服务,并可通过Arm DesignStart™计划而无需预先支付处理器授权费用。 原始设备制造商(Original Equipment Manufacturers)正越来越多地采用定制的系统级芯片(SoC,System-on-Chip),以创造更加小巧、更低成本、更

- 关键字:

BaySand ASIC

- 上周三,美国国防部高级研究计划局(DARPA)宣布,为了帮助人工智能技术获得长足发展,他们即将开展两项新项目,开发新一代计算机芯片。DARPA相信,开发专门应用于人工智能领域的特制芯片将推动该领域的不断发展。

特制芯片

50年来,摩尔定律作为一项基本原理,一直推动着计算机芯片微处理器的发展。 20世纪60年代,英特尔联合创始人Gordon Moore在经过一系列的观察后,得出了一个推测,他推测集成电路上晶体管的数量,约每隔18-24个月便会增加一倍,微芯片的性能也会得到有效的提升。但现在的

- 关键字:

人工智能 ASIC

- 人工智能(AI)现在的热度节节攀升。这项技术存在了数十年之久,一直不温不火,但它最近已经成为数据中心分析、自动驾驶汽车和增强现实等应用的焦点。这项技术怎么就重获新生了呢?在我看来,人工智能迅速走热的趋势是由两种力量所推动的:训练人工智能系统所需要的数据的大爆发和可以大大加快训练进程的新技术的出现。下面,我们分别从这两个方面进行一下解读。

数据就是人工智能世界的货币。没有大量的已知结果,就无法进行推论和机器学习。得益于数据中心领域几个巨无霸的强力推动,各种数据库正处于如火如荼的建设中。谷歌已经积累

- 关键字:

ASIC AI

- 一个好的硬件工程师实际上就是一个项目经理,你需要从外界交流获取对自己设计的需求,然后汇总,分析成具体的硬件实现。还要跟众多的芯片和方案供应商联系,从中挑选出合适的方案,当原理图完成后,你需要组织同事来进行配合评审和检查,还要和CAD工程师一起工作来完成PCB的设计。与此同时,要准备好BOM清单,开始采购和准备物料,联系加工厂家完成板的贴装。” 基本知识 1) 基本设计规范 2) CPU基本知识、架构、性能及选型指导 3) MOTOROLA公司的PowerPC系列基

- 关键字:

PCB ASIC

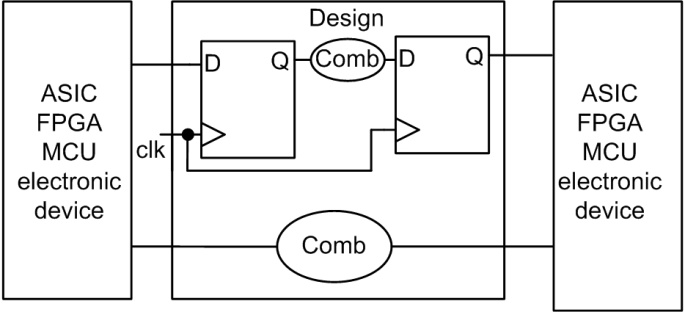

- FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。对于时序如何用FPGA来分析与设计,本文将详细介绍。 基本的电子系统如图 1所示,一般自己的设计都需要时序分析,如图 1所示的Design,上部分为时序组合逻辑,下部分只有组合逻辑。而对其进行时序分析时,一般都以时钟为参考的,因此一般主要分析

- 关键字:

FPGA ASIC

asic ip核介绍

您好,目前还没有人创建词条asic ip核!

欢迎您创建该词条,阐述对asic ip核的理解,并与今后在此搜索asic ip核的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473