- 摘要 IP核的广泛应用提高了电路集成的效率。由于众多功能各异的IP核集成在电路中,完善的测试机制是确保其正常工作的前提。因此,如何对IP核进行测试成为复用IP核技术必须解决的问题。IEEE Std 1500提供了IP核的测试

- 关键字:

IP核 IEEE 1500 Wrapper Hamming码

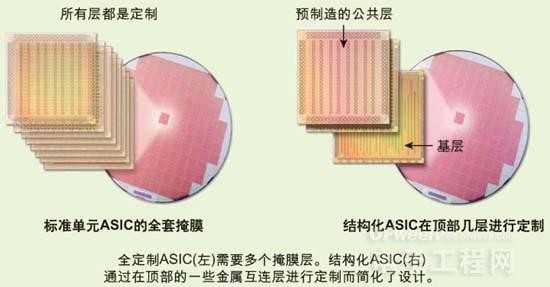

- 作为一个系统设计工程师,经常会遇到这个问题:是选用ASIC还是FPGA?让我们来看一看这两者有什么不同。所谓ASIC,是专用集成电路(Application Specific Integrated Circuit)的简称,电子产品中,应用非常广泛。ASIC的

- 关键字:

FPGA ASIC 系统设计 成本因素

- 我经常收到关于各类设备之间的差异的问题,诸如ASIC、ASSP、SoC和FPGA之间的区别问题。例如是SoC是ASIC吗?或ASIC是SoC吗?ASIC和ASSP之间的区别是什么?以及高端FPGA应该归类为SoC吗?这里有几个难题,至少技术和术语随

- 关键字:

ASIC ASSP SoC FPGA

- 联华电子今(12日)与ASIC设计服务暨IP研发销售厂商智原科技(Faraday Technology Corporation,TWSE:3035)共同发表智原科技于联电55奈米超低功耗製程(55ULP)的PowerSlash™基础IP方案。智原PowerSlash™与联电製程技术相互结合设计,为超低功耗的无线应用需求技术进行优化,满足无线物联网产品的电池长期寿命需求。

智原科技行销暨投资副总于德旬表示:「物联网应用建构过程中,效能往往受制于低功耗技术。而今透过联电55奈

- 关键字:

联华电子 ASIC

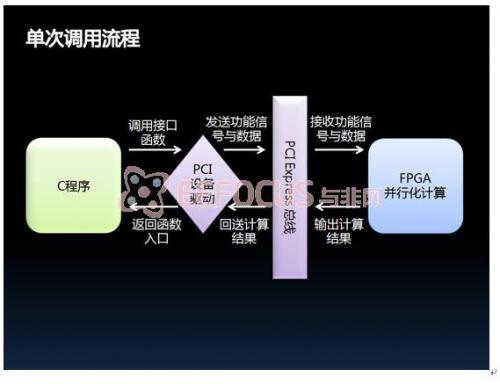

- 摘要 利用FPGA IP核设计了一种快速、高效的傅里叶变换系统。针对非整数倍信号周期截断所导致的频谱泄露问题,提出了一种通过时输入信号加窗处理来抑制频谱泄露的方法。利用Modelsim和Matlab对设计方案进行了仿真,同

- 关键字:

FFT FPGA IP核 加窗处理

- SOPC(System On a Programmable Chip,可编程芯片系统)就是在一个可编程芯片上实现一个电子系统的技术。SOPC是可编程逻辑器件技术和SoC(System on Chip)技术发展与

- 关键字:

Avalon总线 SHT11 温湿度传感器 IP核

- 数字化是电子设计发展的必然趋势,EDA 技术综合了计算机技术、集成电路等在不断向前发展,给电子设计领域带来了一种全新的理念。本文笔者首先简

- 关键字:

EDA ASIC

- 一种CORDIC协处理器核的设计与实现, 随着航天技术的发展,航天任务对于导航计算机的性能要求越来越高。导航计算机除了要对传感器数据进行采集,与控制系统进行实时通讯,还要能进行实时的计算。尽管目前航天任务中使用的处理器芯片性能越来越强,但大多

- 关键字:

FPGA IP核 CORDIC 协处理器

- 本文通过列举Altera 公司的 20nm Arria 10 FPGA 和 Arria 10 SoC (片上系统) 开发电路板的电源管理解决方案,分析了对于FPGA、GPU 或 ASIC 控制的系统中电源管理带来的挑战,并指出通过使用 LTPowerCAD 和 LTPowerPlanner 这类工具,可以大大简化对负载点稳压器以及各部分分析结果的映射任务。

- 关键字:

电源管理 FPGA GPU ASIC 201609

- ASIC 设计服务暨 IP 研发销售领导厂商-智原科技(Faraday Technology, TAIEX: 3035)于日前获颁 ISO9001 Plus 典范奖项。ISO9001:2015是ISO 15年来最大改版,能成为首批获得SGS专业验证的厂商,是对智原在品质承诺、经营与职能发展表现上的高度肯定和最具体验证。

智原科技成立于1993年,累积20余年在 IP (矽智财)与 ASIC 设计服务的丰富经验,不但自主产出了3,000多支的 IP,更有2,000多个专案的成功量产经验,客户遍及台

- 关键字:

ASIC 智原科技

- 联华电子今(3日) 与 ASIC 设计服务暨 IP 研发销售厂商智原科技共同发表智原科技于联电28奈米 HPCU 工艺的可编程12.5Gbps SerDes PHY IP 方案。此次智原成功推出的 SerDes PHY,为联电28奈米 High-K / Metal Gate 后闸极技术工艺平台中一系列高速 I/O 解决方案的第一步。

藉由采用涵盖1.25Gbps 到12.5Gbps 的可编程架构技术,此 SerDes PHY 能够轻易支持10G/1G xPON 被动光纤网络通讯设备。结合不同的

- 关键字:

联华电子 ASIC

- Arasan今日宣布,其MIPI DPHY IP核Ver1.2版本即刻开始供货,该版本在TSMC 28纳米HPC工艺之上可支持高达2.5Gbps的速度。该IP产品将很快被移植到TSMC最新的HPC Plus工艺上。Arasan的MIPI DPHY IP核向下兼容以前的标准版本,需要时能够以1.5Gbps或更低的速度运行。

Arasan提供的最新DPHY IP产品使用了全新的、正在申请专利的DPHY架构,该架构为实现超低功耗和超小面积而优化了DPHY设计。

“我们利用自己在DPH

- 关键字:

Arasan IP核

- 静态时序分析简称STA(Static Timming Analysis),它提供了一种针对大规模门级电路进行时序验证的有效方法。它指需要更具电路网表的拓扑,就可以检查电路设计中所有路径的时序特性,测试电路的覆盖率理论上可以达到100%,从而保证时序验证的完备性;同时由于不需要测试向量,所以STA验证所需时间远小于门级仿真时间。但是,静态时序分析也有自己的弱点,它无法验证电路功能的正确性,所以这一点必须由RTL级的功能仿真来保证,门级网表功能的正确性可以用门级仿真技术,也可以用后面讲到的形式验证技术。值

- 关键字:

fpga asic 静态时序

- 除法,这个小学4年纪就开始学习和使用的方法却一直是我这个ASIC工程师心中的痛。我一直在思考如何能找到一个简单(硬件资源少)而快捷(时钟排数少)的通用除法电路。 其实简单的说除法可以用迭代的减法来实现,但是对于硬件,这恐怕要花很多时间。我也一直没有找到实现任意除法的好方法。但是对于某些除数固定的除法还是有一些办法的。 1)最容易想到的就是ROM查找表,但是ROM毕竟不是我们的目标,虽然ROM有时是不错的方法。 2)我开始仔细考虑这个问题是在做264解码时必须要处理QP的问题。这是一个除以6的计算

- 关键字:

除法电路 ASIC

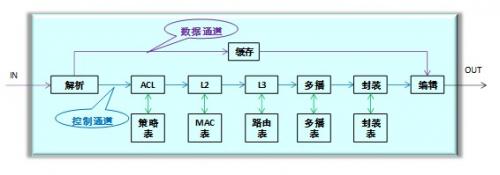

- 2015年10月19日,Mentor Graphics公司今天宣布,推出支持25G、50G和100G以太网的Veloce® VirtuaLAB Ethernet环境。这种支持有助于实现今天正在创建的基于大规模以太网设计的高效的、基于仿真的验证。

连接需求的激增对交换机和路由器设计的尺寸有着深远的影响,使之成为了今天开发的最大的IC设计。设计的绝对尺寸、早期发布的压力,以及需要验证所有路径,都推动着将验证从模拟转向基于仿真流程方法的转变。

Juniper Networks硅和系统工程

- 关键字:

Mentor Graphics ASIC

asic ip核介绍

您好,目前还没有人创建词条asic ip核!

欢迎您创建该词条,阐述对asic ip核的理解,并与今后在此搜索asic ip核的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473