- 张忠谋在当下选择退休可谓急流勇退,在台积电正处于巅峰的时候退休是恰当的时机,但台积电面临挑战其实在张忠谋领导下就已出现。

- 关键字:

台积电,5nm

- 全球第一大芯片自动化设计解决方案提供商及全球第一大芯片接口IP供应商、信息安全和软件质量的全球领导者Synopsys近日宣布, Synopsys 设计平台获得TSMC最新版且最先进的5nm工艺技术认证,可用于客户先期设计。通过与TSMC的早期密切协作,IC Compiler ™ II 的布局及布线解决方案采用下一代布局和合法化技术,最大限度地提高可布线性和总体设计利用率。借助重要的设计技术协同优化工作,通过使用PrimeTime®Signoff和StarRC™提取技术实现ECO闭合,IC Compil

- 关键字:

Synopsys 5nm

- 这两年,三星电子、台积电在半导体工艺上一路狂奔,虽然有技术之争但把曾经的领导者Intel远远甩在身后已经是不争的事实。

- 关键字:

三星 5nm

- 随着5nm工艺制造难度的增加,台积电以及三星电子等巨头研发所耗费的时间势必会增加不少,这也为中芯国际弯道超车提供了一定的机遇。

- 关键字:

台积电 5nm

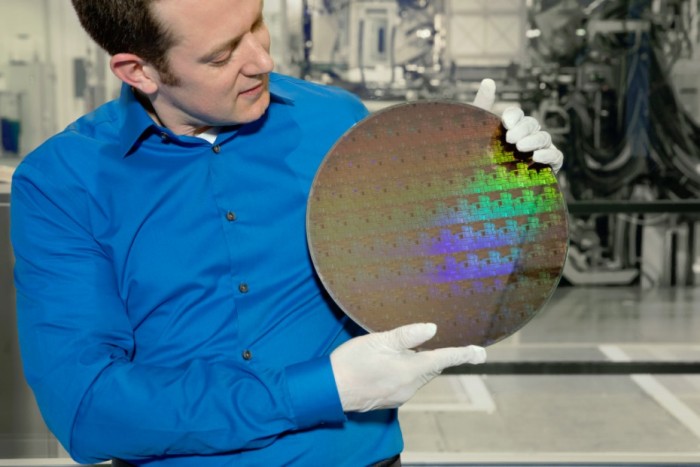

- 据台湾媒体报道,台积电将于本周在台湾南部科学工业园区(STSP)开工建设新的5nm工厂,并将于2020年启动3nm工厂,而新工艺的快速演进将大大巩固台积电一号代工厂的地位。

台积电董事长张忠谋会出席奠基仪式,这也将是他在今年6月份退休之前,最后一次参加这类活动。

目前,台积电正在积极准备量产7nm,预计第二季度即可实现、第四季度火力全开。

更关键的是,台积电已经垄断了7nm代工市场,收获了100%的订单,包括高通骁龙855、苹果A12等重磅大单,彻底击败三星。

根据路线图,台积

- 关键字:

台积电 5nm

- 5nm以下的工艺尺寸缩减逻辑;DRAM、3DNAND和新型存储器的未来;太多可能解决方案带来的高成本。

近日,外媒SE组织了一些专家讨论工艺尺寸如何继续下探、新材料和新工艺的引入带来哪些变化和影响,专家团成员有LamResearch的首席技术官RickGottscho、GlobalFoundries先进模块工程副总裁MarkDougherty、KLA-Tencor的技术合伙人DavidShortt、ASML计算光刻产品副总裁GaryZhang和NovaMeasuringInstruments的首

- 关键字:

5nm DRAM

- 一时之间,仿佛EUV成为了衡量中国半导体设备产业发展水平的标杆,没有EUV就无法实现半导体强国之梦?

- 关键字:

EUV 5nm

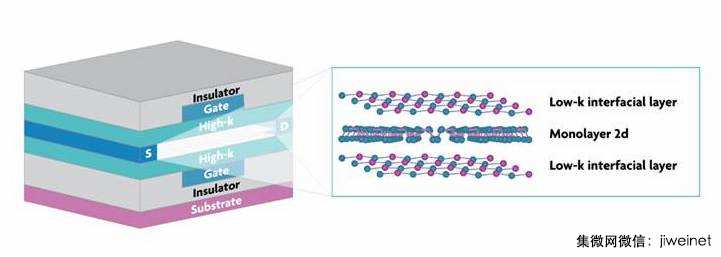

- 根据比利时研究机构Imec指出,设计人员可以选择采用2D非等向性(颗粒状速度更快)材料(如黑磷单层),让摩尔定律(Moore‘s Law)扩展到超越5纳米(nm)节点。Imec研究人员在Semicon West期间举办的年度Imec技术论坛(Imec Technology Forum)发表其最新研究成果。

Imec展示的研究计划专注于实现高性能逻辑应用的场效电晶体(FET),作为其Core CMOS计划的一部份。Imec及其合作伙伴分别在材料、元件与电路层级实现协同最佳化,证实了在传

- 关键字:

Imec 5nm

- Imec 开发下一代 5nm 2D 通道 FET 架构,证实采用 2D 非等向性材料可让摩尔定律延续到超越 5nm 节点…

根据比利时研究机构Imec指出,设计人员可以选择采用2D非等向性(颗粒状速度更快)材料(如黑磷单层),让摩尔定律(Moore's Law)扩展到超越5纳米(nm)节点。Imec研究人员在Semicon West期间举办的年度Imec技术论坛(Imec Technology Forum)发表其最新研究成果。

Imec开发的下一代5nm 2D通道

- 关键字:

摩尔定律 5nm

- 上周,Nvidia CEO黄仁勋在台北电脑展上表示摩尔定律已死(黄仁勋说摩尔定律已死,Nvidia要用人工智能应对),不过IBM和三星有不同意见。

雷锋网消息,日前,IBM联合三星宣布了一项名为nanosheets的晶体管制造技术。该技术抛弃了标准的 FinFET 架构,采用全新的四层堆叠纳米材料。这项技术为研发5nm芯片奠定了基础。IBM表示,借助该项技术,芯片制造商可以在指甲盖大小的芯片面积里,塞下将近300亿个晶体管。要知道,高通不久前发布的采用10nm工艺的旗舰芯片骁龙835,也才不过集

- 关键字:

IBM 5nm

- 据外媒报道,三星联合 IBM 日前宣布了一项名为 nanosheets 的技术。得益于该技术,芯片制造商能够将更多的晶体管容纳到更小的芯片组里,他们宣称在 5nm 芯片可以实现在指甲盖大小中集成 300 亿颗晶体管,而当前 10nm 的骁龙 835 仅仅集成的晶体管数量约为 30 亿。

IBM 称,同样封装面积晶体管数量的增大有非常多的好处,比如降低成本、提高性能,而且非常重要的一点是,5nm 加持下,现有设备如手机的电池寿命将提高 2 至 3 倍。早在 2015 年,IBM 就携手 Glo

- 关键字:

IBM 5nm

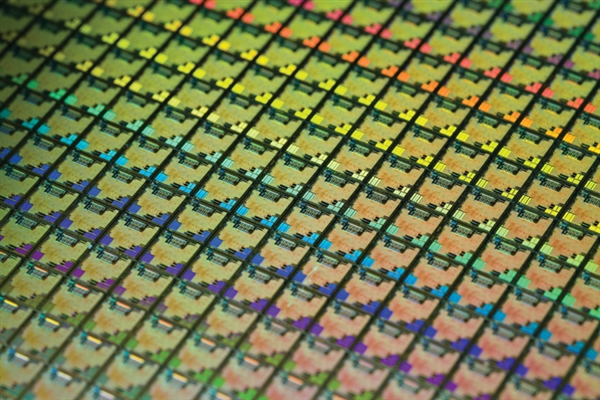

- 晶圆代工龙头台积电年度股东常会将于6月8日登场,并于今(24)日上传致股东报告书,当中揭露先进制程技术最新进展,其中,7纳米已在今年4月开始试产,预期良率改善将相当快速,5纳米则维持原先计划,预计2019年上半年试产。

台积电董事长张忠谋指出,去年间与主要客户及硅智财供应商携手合作完成7纳米技术硅智财设计,并开始进行硅晶验证,按照计划在今年4月试产。

5纳米部分,张忠谋表示,规划使用极紫外光(EUV)微影技术,以降低制程复杂度,制程技术预计2019年上半年试产。

10纳米部分则是已在

- 关键字:

台积电 5nm

- 回顾台媒的这些宣传,只是让大家对台媒在宣传中国台湾的高科技企业的先进技术研发进展时,要进行思考,而不是完全相信,先进技术研发需要大量人力物力,并非一朝一夕可以取得领先优势。

- 关键字:

台积电 5nm

- 台积电物联网业务开发处资深处长王耀东表示,未来台积电成长动能来自于高阶智慧型手机、高效运算晶片、物联网及车用电子。而台积电在10奈米技术开发如预期,今年底可以进入量产,第一个采用10奈米产品已达到满意良率,目前已经有三个客户产品完成设计定案,预期今年底前还有更多客户会完成设计定案,该产品在明年第1季开始贡献营收,且在2017年快速提升量产。

7奈米部分,台积电该部分进度优异,7奈米在PPA及进展时程均领先竞争对手,两个应用平台高阶智慧型手机及高效运算晶片客户都积极采用台积电7奈米先进制程技术,且

- 关键字:

台积电 5nm

- 由IEEEElectronDeviceSociety主办的半导体互连(布线)技术相关国际会议“IEEEInternationalInterconnectTechnologyConference(IITC)2016”于5月23~26日在美国圣荷西举办。这是该会议时隔两年再次回到美国,共有超过230人参加,展开了积极的讨论。

IITC2016的论文数量为一般口头演讲(包括主题演讲)45件,展板发表33件。一般演讲按领域划分,涵盖硅化物的“MUP(Materials

- 关键字:

5nm 布线技

1.5nm介绍

您好,目前还没有人创建词条1.5nm!

欢迎您创建该词条,阐述对1.5nm的理解,并与今后在此搜索1.5nm的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473