基于TMS320 DM642的多路视频处理系统设计

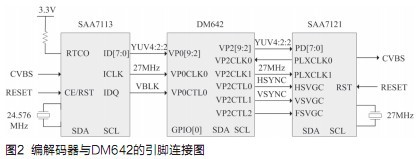

编解码器与DM642的引脚连接图如图2所示。

本文引用地址:https://www.eepw.com.cn/article/95273.htm

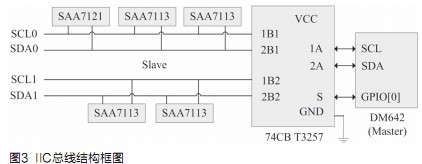

DM642中的IIC接口不支持高速模块[2],因此在本设计中所使用的IIC总线速率最高为400kbit/s。本设计中采用了TI的4bit 2选1切换器SN74CBT3257使DM642可以每次选择接收一组IIC数据。由于SAA7113只能配置两个不同的设备地址,一条I2C总线中不能同时连接4个SAA7113,因此须将IIC总线切分成IIC0和IIC1。具体连接方式见图3。

软件设计

设置DM642内部模块的配置参数,包括VPort视频端口参数配置,SDRAM及FLASH寄存器配置;IIC总线参数配置;编解码芯片内部寄存器配置等。

系统上电初始化,DM642通过内部软件模拟IIC总线时序,配置好SAA7113内部寄存器,设置其工作方式;之后DM642向CPLD发送采集指令,双方通过HOLD、HOLDA握手信号,实现总线控制交接,此时CPLD获得总线控制权,然后打开SAA7113的输出,对采集到的视频数据进行写控制;当一帧视频数据写入SDRAM帧缓存器后,CPLD关闭SAA7113视频输出,放弃总线控制权,并发送中断信号给DM642;DM642重新获得控制权后,对采集到的视频数据使用特定算法进行图像处理,并将处理后的视频数据缓存在SDRAM中,同时配置SAA7121内部寄存器,设置其工作方式,此时将SDRAM中缓存的图像数据送入SAA7121进行D/A转换,并经过并口送VGA显示器进行图像显示;DM642在图像处理完毕后即重新发出开始采集命令,进行下一帧数据的采集。

评论