小梅哥和你一起深入学习FPGA之串口调试(一)(下)

以上为小梅哥为了对特权同学的串口收发模块进行测试所展开的部分工作,到这里,仿真测试所需要的准备工作我们就做好了,接下来将实际进行仿真,通过仿真来分析该模块的性能。

本文引用地址:https://www.eepw.com.cn/article/283060.htm这里极力推荐大家使用modelsim进行仿真,因为quartusII自带的仿真工具灵活性和功能都赶modelsim相差甚远。Modelsim作为一款强大的仿真软件,在业界被广泛使用。同时,modelsim针对不同的EDA厂家,也推出了OEM版本,modelsim-altera就是为Altera公司开发的OEM版本,此版本针对Altera公司的器件预先做了许多的工作,使我们使用的时候能够更加的快捷方便,这里,小梅哥就使用modelsim-Altera版本来仿真这个设计。

我们可以使用modelsim-Altera,通过完全手动化的方式来建立仿真工程,添加仿真库、编译文件,添加波形,运行仿真,当然也可以使用Nativelink的方式,通过quartus II软件实现一键调用,实现自动化的仿真过程。这里,对于初学者,小梅哥还是推荐采用这种自动化的方式,因为简单,不需要过多的手动操作,且不容易出错。这里,小梅哥也使用这种方式来进行仿真。

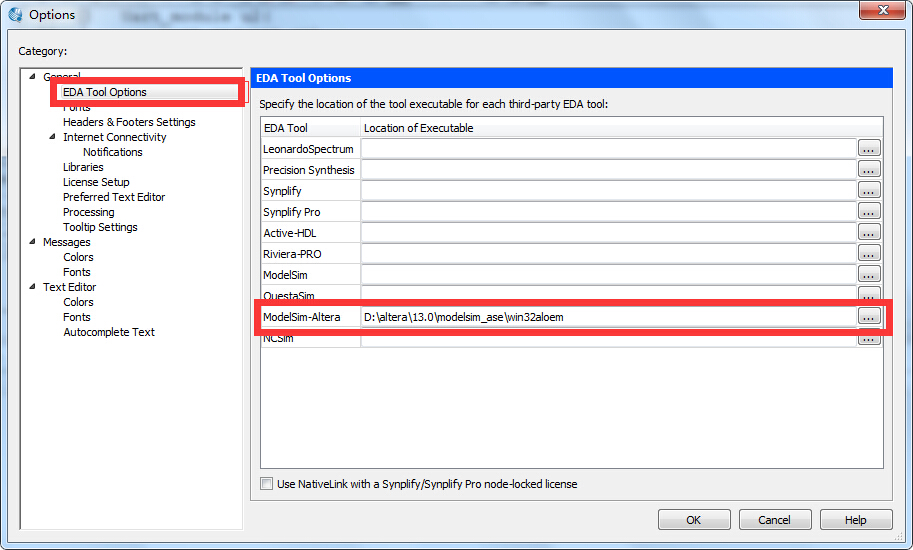

要使用这种方式仿真,我们需要在QuartusII软件中进行EDA Tools的设置。在quartus II软件中,依次点击“tools – options ”,在打开的选项卡中选择“EDA tool options”,在modelsim-altera一栏中输入你的modelsim-Altera的安装路径(部分在安装的时候就已经自动设置好了,就不用去管),如下图所示:

这里设置完成后,点击OK即可。

当确认这一步没有问题后,我们就可以开始进行Nativelink的设置了。Nativelive就是一个链接的过程,通过设置Nativelink,让Quartus II软件能够自动的调用modelsim-altera软件,并建立仿真工程,添加仿真库、编译文件,添加波形,运行仿真。接下来我们就来进行Nativelink的设置

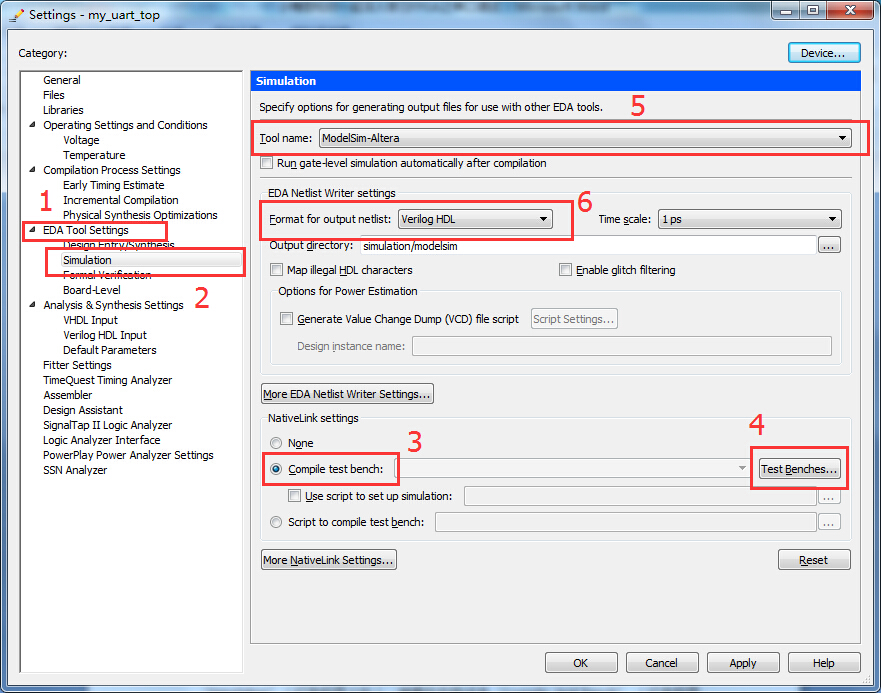

第一步:依次点击“assignments– settings”,

在弹出的选项卡中,选中“EDA Tool Settings”(红色标号1处),在子选项中选择“Simulation”(红色标号2处),注意红色标号5处和6处应分别选择为modelsim-altera和Verilog HDL,如果不是,请通过下拉列表选择为上述选项。点击“Compile test bench” (红色标号3处),然后点击最右侧的“Test Benchs” (红色标号4处),就会弹出如下所示的界面:

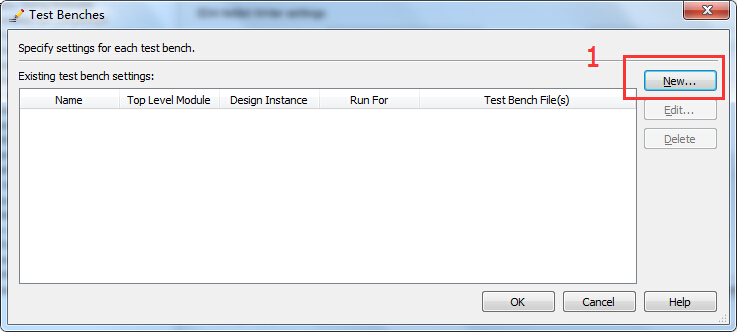

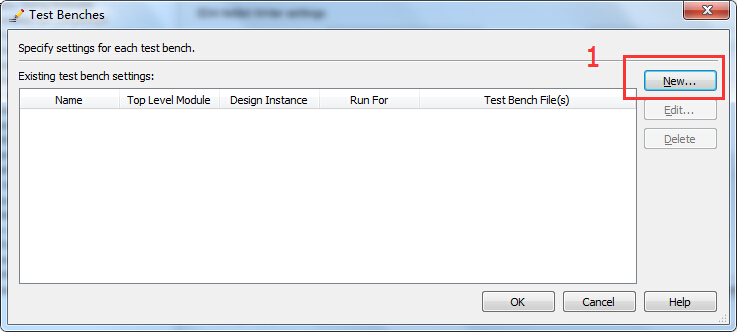

点击“New” (红色标号1处),接着会弹出“New Test Bench Settings”界面,如下图所示:

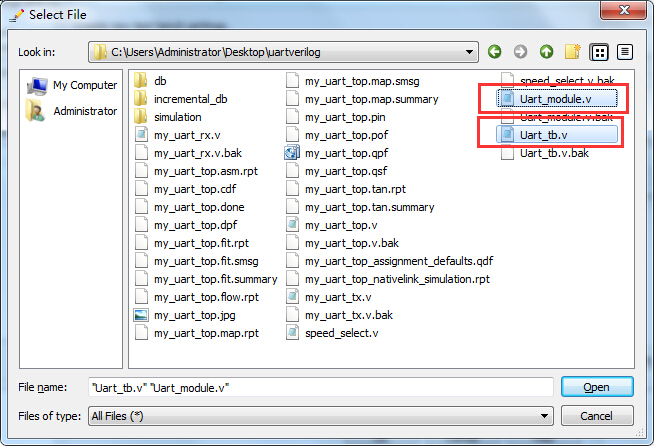

首先我们点击红色标号1处的三个小点,在弹出的文件选择界面中,选中我们需要加入的testbench文件,如下所示:

这里我们选择“Uart_tb.v”和“Uart_module.v”,点击“Open”打开。这里,“Uart_tb.v”为仿真顶层文件,“Uart_module.v”为串口仿真模型。

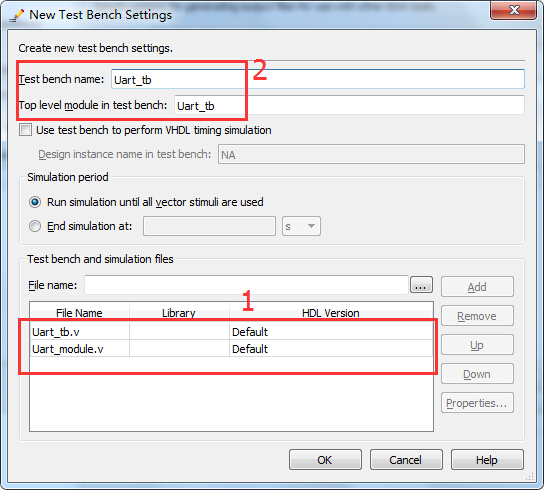

文件选择好之后,回到New Test Bench Settings界面,如下图所示,

在顶端“test bench name”(红色标号2)处输入我们的仿真顶层文件名,即Uart_tb,注意,不要加“.v”后缀。于是,”Top level module in test bench”会自动与“Test bench name”保持一致。

至此,我们的Nativelink设置就完成了,一路选择OK下去,直到回到Quartus II软件的主界面。此时,我们已经完成了仿真需要的所有设置,我们直接点击Quartus II软件上的RTL Simulation图标

即可启动仿真,也可以通过“Tools– Run Simulation Tool – RTL Simulation”启动仿真。

接下来,我们需要做的就是大约20秒左右的等待,这个过程中,Quartus II会自动启动modelsim-altera软件,建立仿真工程,添加仿真库、编译文件,添加波形,运行仿真。最后停留在如下所示的状态:

这里,右侧深色窗口为波形窗口,下方为副本界面,打印了软件运行过程中的信息,包括添加文件、编译文件、添加波形、运行等,同时还打印了testbench中需要打印输出的信息。具体的打印信息如下:

由此打印信息可知,串口仿真模型总共进行了8次数据发送,却只收到了6次数据,因此有两次发送给串口模块的数据丢失或者串口模块发送的数据不正确。同时,第一次发送出去的数据接收回来还是正确的,但是第二次发送的数据再接收回来,就错误了。这两次数据发送之间的时间间隔为40ns。考虑可能是发送间隔太短导致,但是当第4次发送的数据(s4)被正确接收后(r3),紧接着第5次发送的数据在发回的时候,再次出错,而s4和s5之间间隔了300ns,因此可知,该串口收发模块在连续两次发送间隔很短的情况下,很容易出错。那么,怎么样才能保证连续两次发送之间,即使很短的间隔,也不出错误呢?小梅哥通过对仿真波形的分析发现:一次接收数据,总共有12个波特率脉冲,如下图所示:

这里小梅哥就有点疑惑了,我们一般的应用中,串口一帧的数据为十位,包含1位起始位、8位数据位、一位停止位,一般不含校验位。因此,这里明显多了两个波特率周期,那么,问题很有可能就出在这里。回到这部分的代码:

43 always @ ( posedge clk or negedge rst_n )

44 if(! rst_n ) begin

45 bps_start_r <= 1'bz ;

46 rx_int <= 1'b0 ;

47 end

48 else if( neg_rs232_rx ) begin

// rs232_rx

49 bps_start_r <= 1'b1 ; //

50 rx_int <= 1'b1 ; //

51 end

52 else if( num==4'd12 ) begin //

53 bps_start_r <= 1'b0 ; //

54 rx_int <= 1'b0 ; //

55 end

56

57 assign bps_start = bps_start_r ;

58

59//---------------------------------------------------------

60 reg[ 7 : 0] rx_data_r ; //

61 //---------------------------------------------------------

62

63 reg[ 7 : 0] rx_temp_data ; //

64

65 always @ ( posedge clk or negedge rst_n )

66 if(! rst_n ) begin

67 rx_temp_data <= 8'd0 ;

68 num <= 4'd0 ;

69 rx_data_r <= 8'd0 ;

70 end

71 else if( rx_int ) begin //

72 if( clk_bps ) begin

// , 8bit 1 2

73 num <= num+1'b1 ;

74 case ( num)

75 4'd1:rx_temp_data[0] <= rs232_rx; // 0bit

76 4'd2:rx_temp_data [1] <= rs232_rx; // 1bit

77 4'd3:rx_temp_data [2] <= rs232_rx; // 2bit

78 4'd4:rx_temp_data [3] <= rs232_rx; // 3bit

79 4'd5:rx_temp_data [4] <= rs232_rx; // 4bit

80 4'd6:rx_temp_data [5] <= rs232_rx; // 5bit

81 4'd7:rx_temp_data [6] <= rs232_rx; // 6bit

82 4'd8:rx_temp_data [7] <= rs232_rx; // 7bit

83 default : ;

84 endcase

85 end

86 else if( num == 4'd12 ) begin//我们的标准接收模式下只有1+8+1(2)=11bit的有效数据

87 num <= 4'd0 ; // STOP ,num

88 rx_data_r <= rx_temp_data ; // rx_data

89 end

90 end

评论