基于STM32的双路信号源及配置平台设计

1.2 系统方案

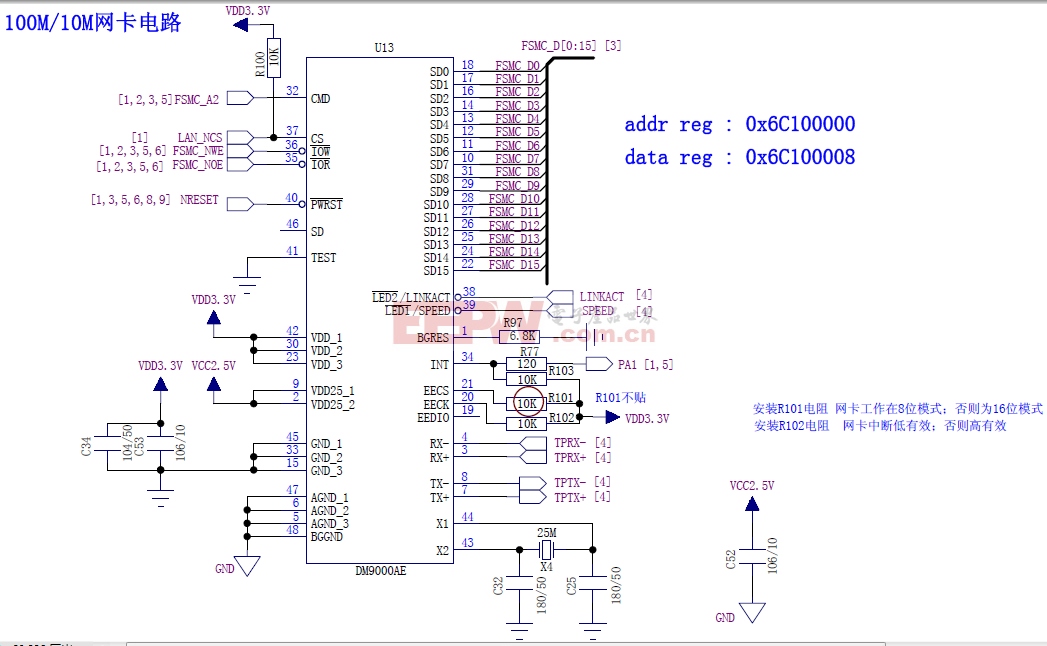

本文引用地址:https://www.eepw.com.cn/article/277033.htm整个信号源系统主要由STM32控制器、AD9958、输出电路、滤波电路、外围电路和上位机配置软件等构成。系统框图如图3所示。

图3 系统方案框图

上 位机控制软件将需要配置(或读取)的参数以命令的方式发送到控制器,控制器解析命令后完成对芯片的配置或读取相应的参数回发到上位机。系统采用双通道 DDS器件AD9958为频率发生器,该器件由两个DDS内核构成,频率、幅度、相位控制字位宽分别为32bit、10bit、14bit,可满足高分辨 率信号需求。每个通道可提供独立的频率、幅度和相位控制,具有卓越的通道隔离度(大于72dB)。由于两个通道采用相同系统参考时钟,因此两个通道间具有 内在的同步性,通过菊花链连接方式可实现多个器件间同步。AD9958另外一个突出的优点是低功耗,在具有多通道DDS器件中,其功耗是最低的。通过外部 控制引脚(PWR_DWN_CTL)和内部可配置寄存器FR1[7:6]、CFR[7:6],实现多种低功耗工作模式。

2 滤波器及AD9958输出电路设计

2.1 LC椭圆低通滤波器的设计

DDS数字式的结构特点也带来了输出杂散的问题。杂散的来源有:

1)DAC输出非理想。

2)参考时钟。

3)幅度量化误差。

4)相位截断。

相位截断杂散以及与相位—幅度转换过程相关的杂散是DDS设计中的有限相位和幅度分辨率造成的结果,对于高性能DDS可以忽略,因而杂散的主要来源是DAC非理想和参考时钟。其中DAC输出功率与量化噪声比可用下式计算:

式中SQR为信噪比,B为DAC分辨率位宽,FFS为DAC输出满量程分数(常见值为1/2,1/4,1/8/,1/16)。

在时钟为300MHz,输出为80MHz时,DAC采样输出幅度谱如图4所示。

图4 采样输出谱分析

对AD9958器件模型进行仿真分析,在无输出滤波器条件下得到的仿真结果如图5所示。

图5 直接输出频谱及时域波形

模拟信号相关文章:什么是模拟信号

尘埃粒子计数器相关文章:尘埃粒子计数器原理

评论