中频软件无线电系统的FPGA实现方案

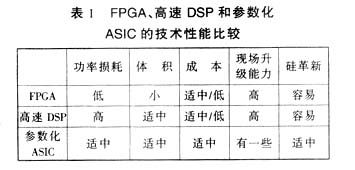

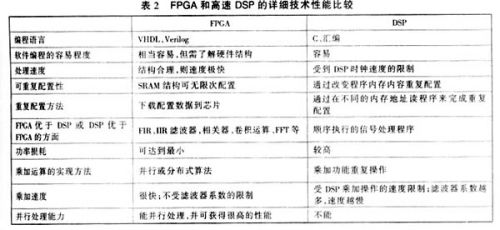

本文采用FPGA来实现中频软件无线电。表1和表2所示的比较分析表明,FPGA与参数化ASIC、DSP比较有很多优势,它不但在功耗、体积、成本方面优于参数化ASIC、DSP,而且处理效率高、现场可编程性能良好。不同于DSP的单流处理方式,FPGA是多流并行处理,这种处理方式使FPGA能完成DSP难以实现的许多功能,如FIR/IIR滤波器、扩频、跳频模式。因此,FPGA能很好地体现软件无线电的灵活性和开放性,很适合在软件无线电中做高速数字信号处理,是实现中频软件无线电的理想选择。

4.采用FPGA实现中频软件无线电系统

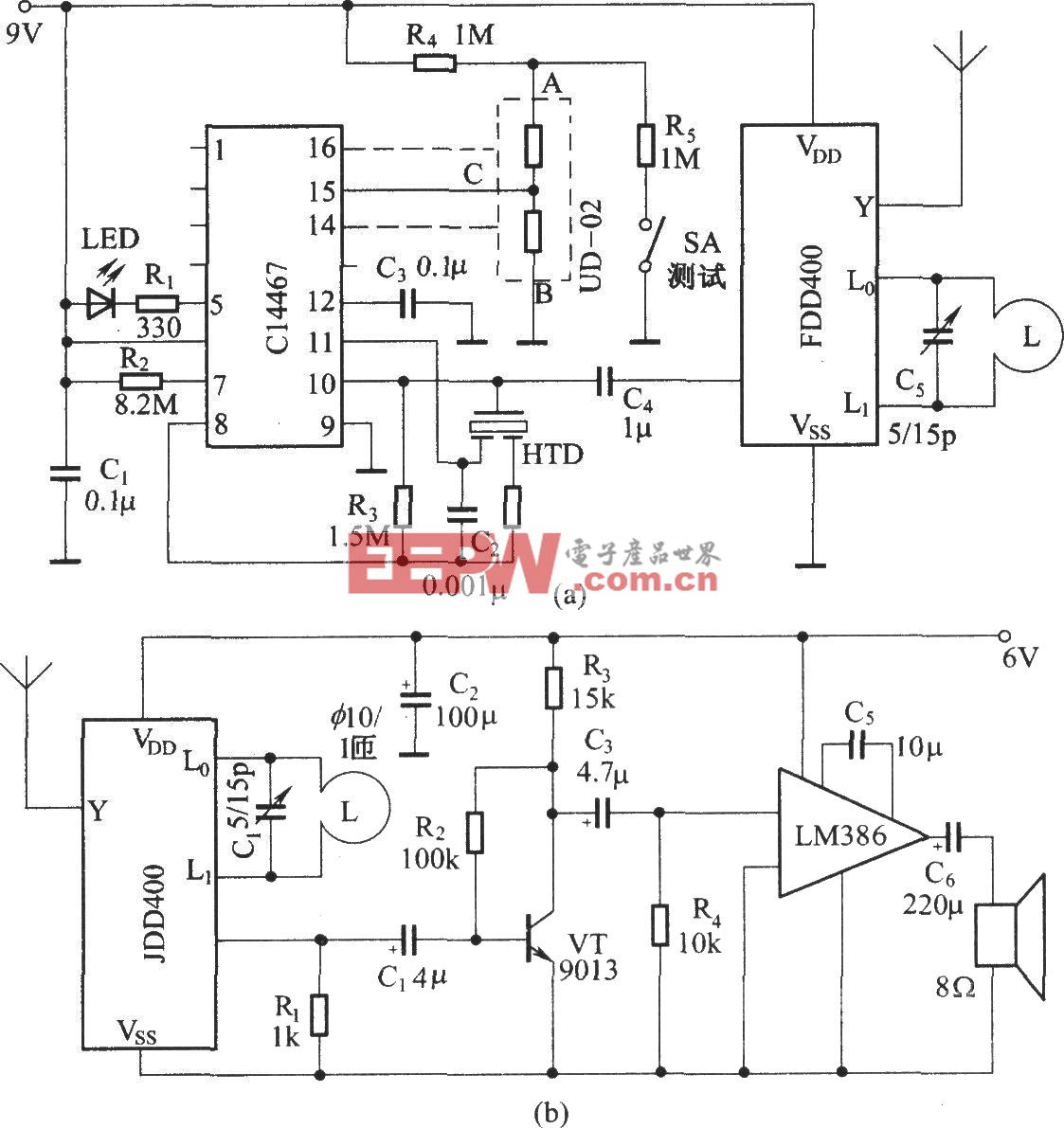

图3为所实现的中频软件无线电系统框图。系统从IF(中频)进行A/D和D/A变换。下面就系统的各部分做一介绍。

1 宽带D/A和A/D转换器

D/A和A/D转换器分别把中频数字信号转换成模拟信号,中频模拟信号转换成数字信号。D/A变换器和A/D变换器的选择,直接关系到软件无线电的总体性能。因此,必须根据系统的要求,综合考虑D/A变换器和A/D变换器的各方面性能,做出选择。

(1)宽带D/A转换器

选用了AD公司的AD9713B,性能指标如下:

1)具有12 bit精度;

2)转换速率最快为80 MSPS;

3)SFDR(无杂散动态范围)为70 dBc。

这里,DAC锁存时钟为40 MHz。AD9713B后接两级放大器,将模拟信号放大后输出。

(2)宽带A/D转换器

在软件无线电中,对ADC的性能要求很高,ADC的选择比DAC更为重要。选择ADC时,需要考虑其采样频率、带宽、转换位数和SFDR。而这几个性能指标是互为约束的,必须综合考虑确定。

在此,ADC选用AD公司生产的AD9042。AD9042是高速、高性能、低功耗的单片12位模/数变换器,其性能指标如下:

1)最大采样速率41 MSPS;

2)SFDR为80 dBc;

3)信噪比为68 dB。

实际使用中,采样时钟为40 MHz,AD9042的性能很好。

2 FPGA——数字信号处理模块

FPGA选用了Altera公司的APEX EP20K200E器件,这个器件为20万门容量,1.8 V低功耗,具有多种I/O接口和多钟配置方式的单片系统级集成的可编程逻辑器件。

FPGA主要完成数字上/下变频、滤波、调制/解调、扩频/解扩、载波以及PN(伪随机码)的同步和跟踪等功能。

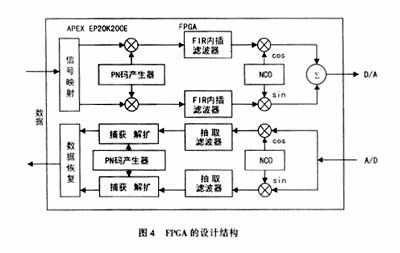

FPGA的设计结构如图4所示。在此,以DSSS(直接序列扩频)信号为例说明。发射的设计为,系统将125 kbit/s的数据映射成上下支路各62.5 kbit/s的数据与PN码产生器输出的4Mchip/s的PN码相乘扩频,然后由14 bit 的FIR滤波器完成内插滤波,滤波器输出的信号为20 MHz,与NCO相乘上变频至中频,并取高12 bit输出至D/A变换器。接收的设计与发射相对应,A/D变换器输出的40 MHz的12 bit中频数字信号与NCO相乘正交下变频成I、Q两路信号,这2路信号经抽取滤波变为20 MHz的基带信号,输入到解扩电路完成PN码的捕获、解扩(用[HJ71mm]匹配滤波器相关器实现)以及信号相关后的功率检测,解扩后的信号和检测到的功率信号输入到码跟踪电路完成码元跟踪,最后完成解码,恢复数据。完成这些功能,所占的FPGA资源为:7142个LE(逻辑单元),16896 ESB(嵌入式逻辑块) bits。

dc相关文章:dc是什么

fpga相关文章:fpga是什么

评论