认知无线电的频谱检测的FPGA实现

初步拟定硬件方案

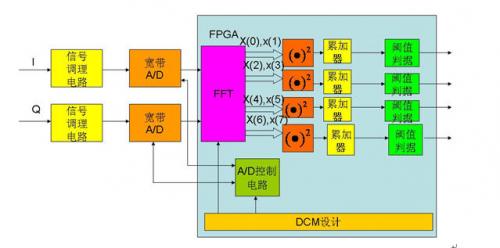

本文引用地址:https://www.eepw.com.cn/article/269587.htm(1)整体方案框图

本次设计使用8点的FFT设计,因此我们需要3级基2点的FFT运算,共有4个旋转因子需要存储,依据项目难点我们主要对FFT模块的设计进行逐层细化:

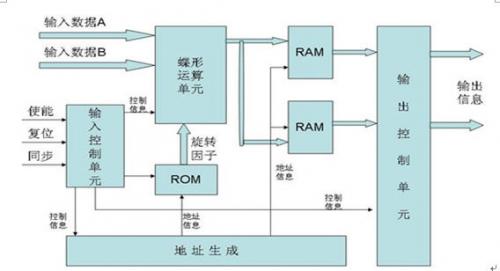

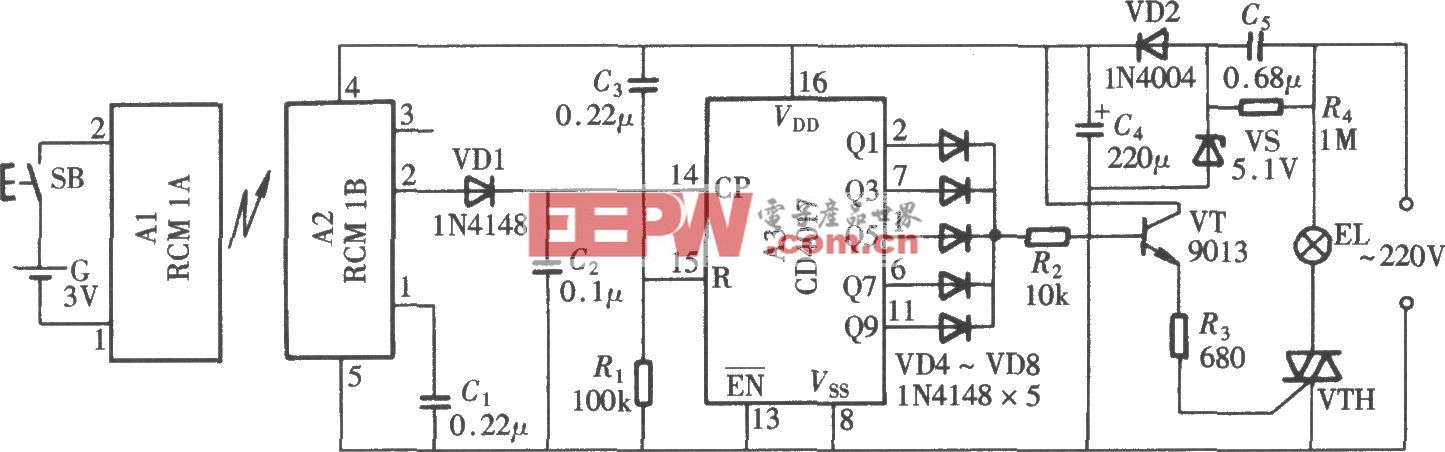

(2)一级FFT的系统框图实现

该框图为一级FFT的系统框图,输入数据A对应I信号的输入,输入数据B对应Q信号的输入,然后对其做基2点的FFT运算。

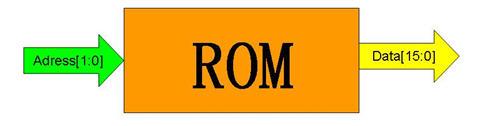

(3)ROM的设计

本次设计为8点FFT运算,就需要4个旋转因子,旋转因子的实部和虚部都采用八位二进制数来表示,因此使用一个宽度为16,深度为4的ROM存储器存储旋转因子。

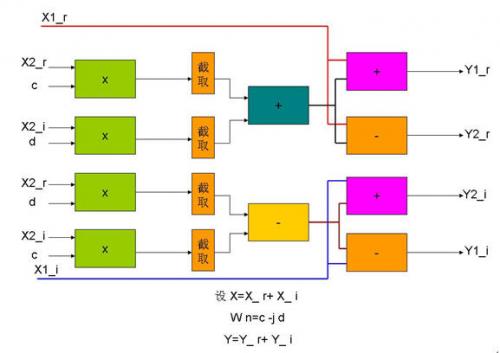

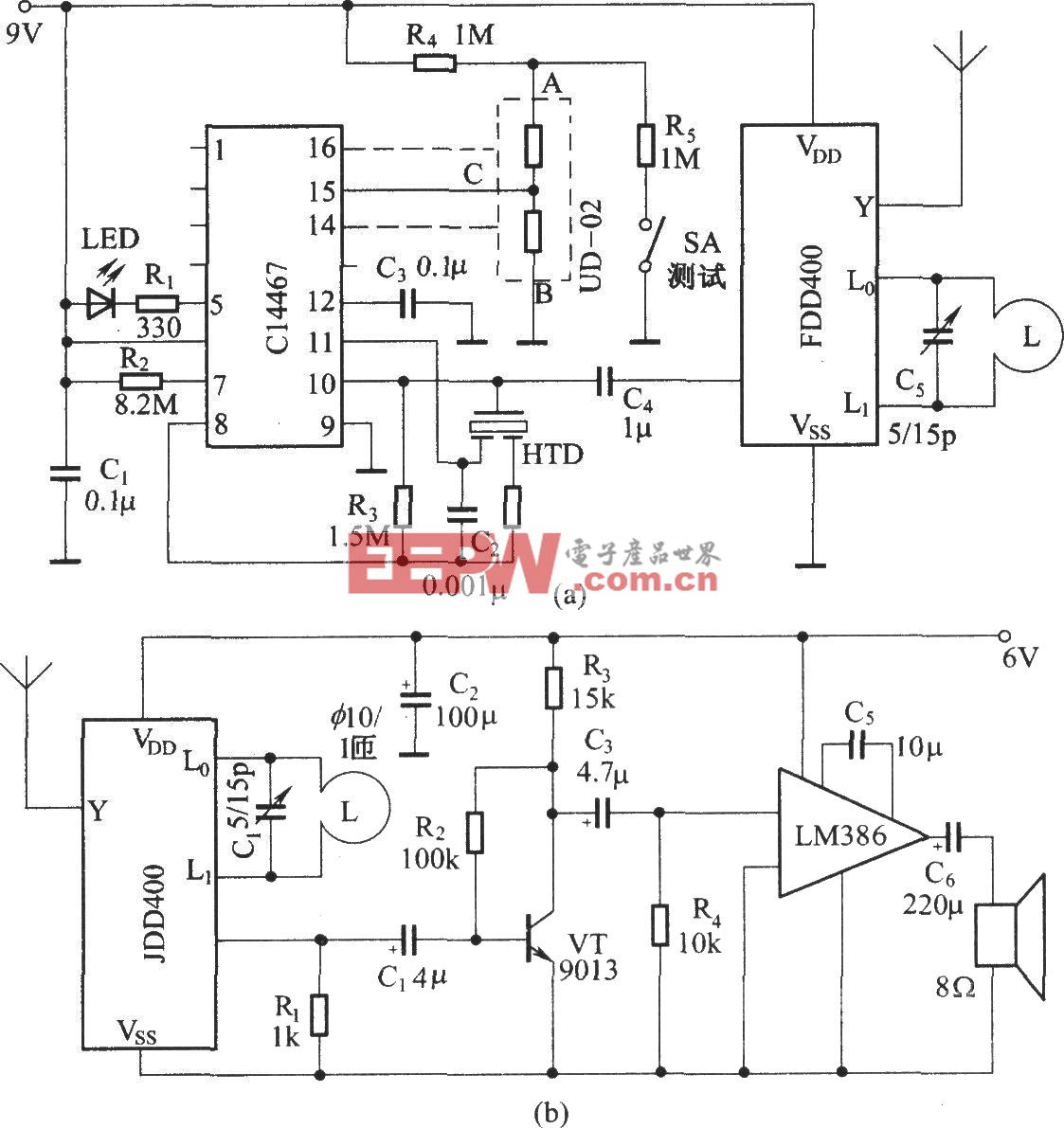

(4)蝶形运算单元的FPGA实现

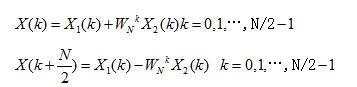

依据蝶形运算公式:

我们得到蝶形运算单元框图为:

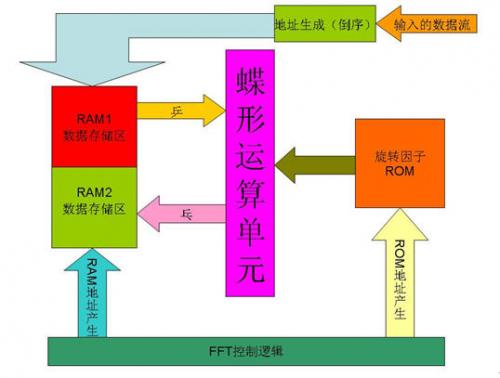

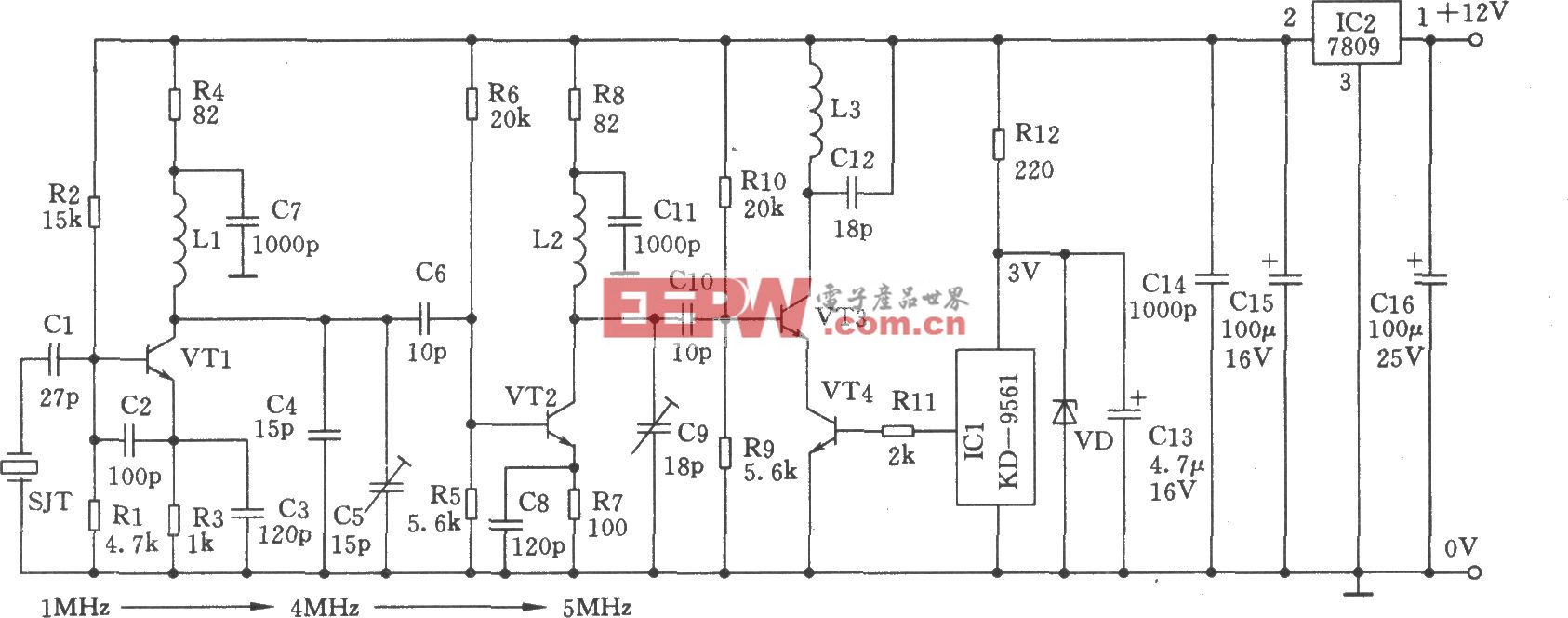

(5)乒乓结构的RAM示意图

我们在FFT模块中开辟两个RAM数据存储区,以此组成典型的乒乓操作模式;在FFT第一级运算中,数据从RAM1经蝶形运算单元计算存入RAM2,在第二次中则正好相反,以此类推…….,下图给出了乒乓结构的RAM示意图。

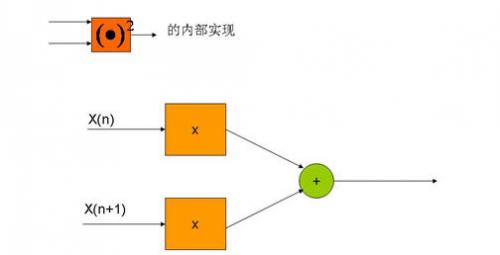

(6)能量求和模块

最终输出信号为:y=x(n)*x(n)+x(n+1)*x(n+1);

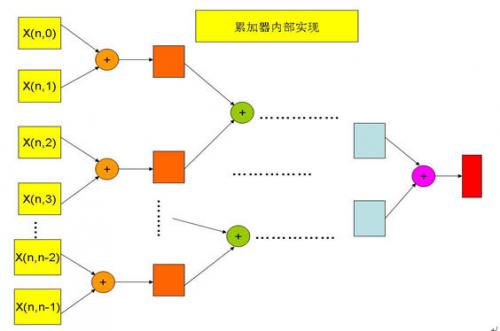

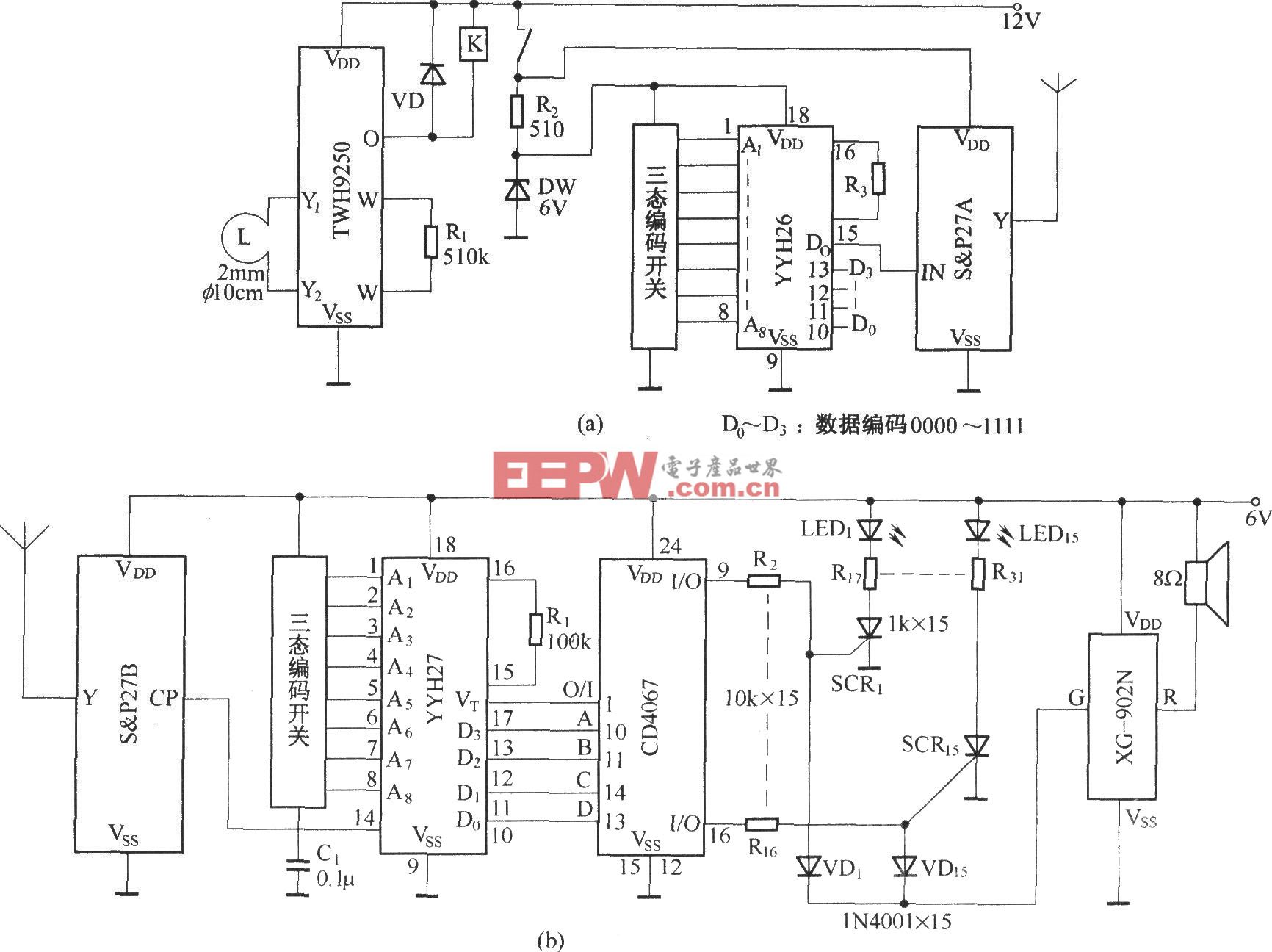

(7)累加电路模块

我们将能量计算模块计算出的能量值通入一个长度为n的FIFO结构,每当FIFO结构中有一个数据量发生变化时,累加器都要进行计算更新,这样就做到了实时监测该通道的频谱占用情况。在累加器当中,为了计算速度足够的快,可以满足实时性要求,我们往往设计为流水线结构。如下图所示:以流水线结构实现的累加器

fpga相关文章:fpga是什么

评论