FPGA设计开发软件ISE使用技巧之:片上逻辑分析仪(ChipScope Pro)使用技巧

表6.4 触发条件判断单元的类型

本文引用地址:https://www.eepw.com.cn/article/269338.htm类 型数值类型匹 配 功 能Bit/Slice说 明

Basic0、1、X=、<>8用于一般信号比较,是一种节约资源的类型

Basic(w/trans)0、1、X、R、F、B=、<>、transition detection4用于控制信号的比较,可以检测跳变的发生

Extend0、1、X=、<>、>、>=、<、<=2当主要考虑数据的大小时,用于地址或数据信号大小的比较

Extend(w/trans)0、1、X、R、F、B=、<>、>、>=、<、<=、transition detection2当数据和地址信号的大小和跳变都需要考虑时,可以用于检测跳变的发生

Range0、1、X=、<>、>、>=、<、<=、in range、not in range1当数据和地址的大小需要考虑时,可以用于检测数值是否在一定范围内

Range(w/trans)0、1、X、R、F、B=、<>、>、>=、<、<=、in range、not in range、transition detection1当数据和地址的大小和跳变都需要考虑时,可以用于检测跳变和数值是否在一定范围内

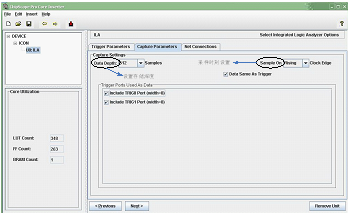

“Capture Parameters”选项卡可以对存储深度、采样时刻等参数进行设置,如图6.43所示。

图6.43 “Capture Parameters”选项卡设置

所谓存储深度,是指在满足触发条件后,要存储多少数据,用于最终的波形显示。ChipScope Pro可能的最大存储深度为16384,最大数据位宽为256bit。实际的数据存储深度和位数由FPGA内部剩余的BlockRam的数量决定。

对于“Data Same As Trigger”选项,有时要观测的信号就是设置的触发条件中的信号,此时选中此项即可。有时设定了触发条件后,想观察别的数据信号,这时可以不选中此项,数据与触发信号完全独立。

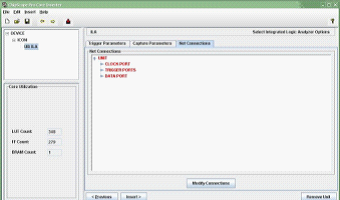

“Net Connections”选项卡可以设置触发端口信号线与要观测的信号的连接,要观测哪些信号,就将这些信号与端口的信号线连接即可,如图6.44所示。

图6.44 “Net Connections”选项卡设置

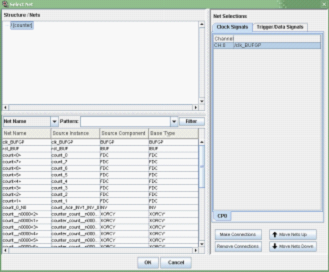

设置的连接信号可以分为3类:时钟信号(CLOCK PORT)、触发端口信号(TRIGGER PORTS)和数据信号(DATA PORT)。单击“Modify Connections”按钮会出现如图6.40所示对话框。

图6.45 网线连接对话框

设置完所有信号后,端口名字会变为黑色,否则为红色。设置完上述各项后,单击“Inserter”按钮,逻辑分析仪的网表就插入到原来的设计网表当中。之后在ISE下完成布局布线并下载后,就可以用ChipScope Pro Analyzer进行观测了。

6.7.4 ChipScope Pro Analyzer简介

将逻辑分析的核插入设计当中后,就可以运行ChipScope Pro Analyzer进行观测了,ChipScope Pro Analyzer的启动方式有两种。

(1)直接运行“开始”/“程序”/“ChipScope Pro 8.2i”/“ChipScope Pro Analyzer”。

(2)在ISE下启动。

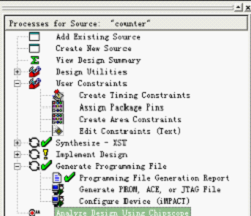

如图6.46所示,双击“Analyze Design Using ChipScope”即可启动,ChipScope Pro Analyzer界面如图6.47所示。

图6.46 从ISE中直接启动ChipScope Pro Analyzer

图6.47 ChipScope Pro Analyzer用户界面

ChipScope Pro Analyzer使用步骤如下。

1.单击![]() 图标,打开JTAG并口连接电缆

图标,打开JTAG并口连接电缆

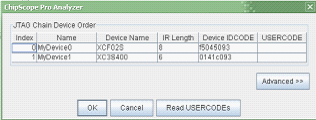

在此之前要保证已将JTAG与器件连接好,如果连接无误,会出现如图6.48所示的对话框。

对话框中会显示JTAG连接的FPGA类型和所用的配置器件类型,这里使用的FPGA为Spartan 3系列,配置器件选用的是XCF02S。

图6.48 JTAG正常连接后提示

2.下载配置文件

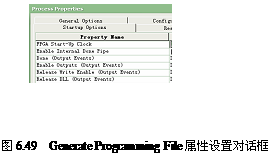

在ISE下完布局布线后,生成配置文件*.bit文件。注意:ChipScope Pro采用JTAG方式观测FPGA内部信号,这就要求在生成下载文件时。在“Generate Programming File”的属性对话框(如图6.49所示)中设置“Startup Options”/“FPGA Start-Up Clock”为JTAG Clock,否则ChipScope Pro将无法正确配置器件。

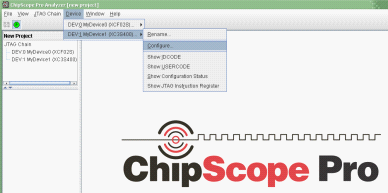

下载配置文件时,选择“Device”/“DEV1”/“Configure”选项,如图6.50所示。单击后会出现如图6.51所示的对话框,选择要下载的*.bit文件,对FPGA进行配置。

图6.50 配置FPGA

图6.51 选择配置文件对话框

3.设置触发条件

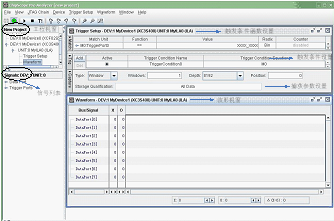

成功完成对FPGA的配置后,会出现如图6.52所示界面。

图6.52 成功完成配置后用户界面

如图6.52所示,ChipScope Pro Analyzer的界面由两部分组成。

左边一栏为工程视窗和信号列表。工程视窗的下拉列表中有“Trigger Setup”、“Waveform”选项。双击后,就会有相应的视窗在右边显示。信号列表中列出了所有信号,在这里可以增加或删除视图中的信号,对信号重命名,也可以将信号组合为总线以便于观察。

fpga相关文章:fpga是什么

评论