FPGA设计开发软件ISE使用技巧之:增量式设计(Incremental Design)技巧

对于VHDL来说,XST可以自动检测出哪一个逻辑分组的内容发生了改变。但对于Verilog来说,必须应用“resynthesize”属性。例如下面就是一个逻辑分组A的Verilog源代码发生细微的改变时的XCF文件范例。

本文引用地址:https://www.eepw.com.cn/article/269337.htmMODEL "top" incremental_synthesis = yes; //对top使能增量设计

MODEL "A" incremental_synthesis = yes; //对A使能增量设计

MODEL "B" incremental_synthesis = yes; //对B使能增量设计

MODEL "C" incremental_synthesis = yes; //对C使能增量设计

MODEL "top" resynthesize = no; //通知综合工具哪个模块发生改变

MODEL "A" resynthesize = yes; //no为未改变,yes为已改变

MODEL "B" resynthesize = no;

MODEL "C" resynthesize= no;

对于Verilog设计工程,当某一逻辑分组发生改变时,要为其附加相应的综合约束,才能实现增量综合。

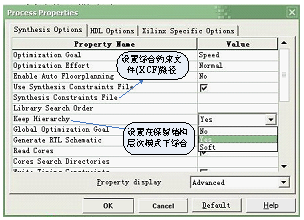

另外需要注意的问题是,增量综合是在保留结构层次模式(Keep Hierarchy)下完成的,在进行增量综合时,在“Processes for Source”中选择“Synthesize-XST”,单击右键,设置综合属性如图6.30所示。

如图6.30所示,要完成增量综合,要完成两种设置,选择“Keep Hierarchy”设置为YES或Soft,选择“Synthesis Constraints File”设置综合约束文件的路径。

增量综合后,需要检查综合报告。

图6.30 增量综合属性设置对话框

3.创建区域分组约束

创建区域分组约束是增量设计中最重要的一步。区域分组约束做得不好会增加综合、布局布线耗时,甚至有可能导致布局布线无法完成。区域分组约束的创建是利用ISE下的PACE工具,在PACE下完成区域分组约束后,ISE会自动将其写入UCF文件中。

为增量设计创建合理的区域分组约束要遵循以下原则。

· 所有I/O引脚位置必须锁定。

· 将与I/O端口联系密切的区域分组布置在相应I/O端口的附近。

· 区域分组约束的范围不应该重叠。

· 尽量保证每个区域的资源利用率基本一致,避免出现某一区域利用率达到99%,而另一区域的利用率只有10%的情况。

· 如果一个区域分组中包含FPGA的多种资源,如:Slice、Block RAM、TBUF、Multipliers等,这时很有必要将不同的资源设置在不同的区域,然后将几个不同位置区域拼合为一个区域分组。可以使用PACE、Floorplanner等工具完成,也可以在约束文件中使用如下约束:

INST Logic_Group_A AREA_GROUP = AG_Logic_Group_A ; //AREA分组

AREA_GROUP "AG_Logic_Group_A" RANGE = SLICE_X0Y20:SLICE_X20Y30 ;//SLICE约束

AREA_GROUP "AG_Logic_Group_A" RANGE = RAMB16_X0Y2:RAMB16_X0Y2 ;//RAM约束

AREA_GROUP "AG_Logic_Group_A" RANGE = MULT18X18_X0Y1:MULT18X18_X0Y1;//MULT约束

AREA_GROUP "AG_Logic_Group_A" RANGE = TBUF_X0Y0:TBUF_X1Y0; //TBUF约束

4.增量实现(Incremental Implement)

第3步的创建区域分组约束也可以作为增量实现的内容,增量实现的步骤如下。

(1)设置区域分组约束。

(2)映射、布局布线得到初始指引文件。

(3)下载调试,需要修改时,对细微细节进行修改,然后实现增量综合。

(4)增量综合后在初始指引文件下进行第二次映射与布局布线。

(5)下载调试,如仍有问题,重复步骤(3)~步骤(5),直到符合设计要求为止。

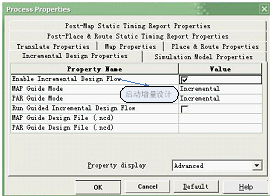

在增量实现过程中,必须要对布局布线的属性进行相关的设置。首先应该使能增量设计,具体设置如图6.31所示。在“Processes for Source”中选择“Implement Design”,单击右键,出现属性对话框。选择“Incremental Design Properties”,然后选择“Enable Incremental Design Flow”,使能增量设计。

图6.31 项目管理器中启动增量设计功能对话框

在增量设计中,如果是用Synplify/Synplify Pro等第三方综合工具,那么需要由综合工具生成向导文件指导实现工具进行实现流程。选择如图6.31中的“Run Guided Incremental Design Flow”选项,表示将由指定的向导文件来指导实现工具进行实现流程。

向导文件可提供Map.ncd文件和Par.ncd文件。其中,Map.ncd文件包含了slices、IOBs等映射信息。Par.ncd文件包含了布局和布线信息。实现工具根据这两个文件的信息来确定没有改变的模块和已经改变的模块,把没有改变的模块放进向导文件所记录的上次综合实现的位置。对布线器来说,该布线资源同时也将被保留,其布线关系也不会改变。

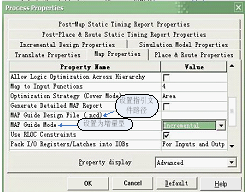

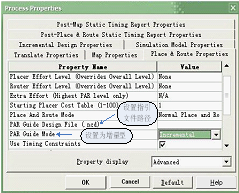

使用向导文件,要对实现具的属性做部分修改。将“Map Guide Mode”和“PAR Guide Mode”分别改成增量型(Incremental),如图6.32和图6.33所示。

图6.32 使用指引文件指引映射 图6.33 使用指引文件引导布局布线

进行了上述设置后,需要指定映射和布局布线的指引文件。

整个增量实现步骤完成后,需要检查映射报告(扩展名为map)和布局布线报告(扩展名为par),看是否真的完成了增量设计。

6.6.3 小结

本节对增量式设计方法的概念以及设计流程做了全面的介绍,希望读者能够掌握增量设计的基本流程,并应用到自己的工程设计当中。在6.9节中会通过一个具体的实例来说明增量设计的整个流程。

增量设计在大型的工程设计中是很有用的,可以为设计节约大量的时间。增量设计中一个难点在于分组区域约束的设置,这不但需要对整个工程有全面的把握而且要求对于FPGA器件的内部结构有一定的了解,这需要在实践中不断积累经验。

fpga相关文章:fpga是什么

评论