京微雅格FPGA的仿真方法

在用Primace调用Moldesim进行仿真时,如果需要更改代码重新编译仿真,每次都去点击Flow->Simulation->RTL Simulation进行仿真,会比较麻烦。其实在连续改代码并生新仿真的过程中,可以按以下步骤进行:

本文引用地址:https://www.eepw.com.cn/article/268186.htm1、 工程第一次可以运行Flow->Simulation->Timing Simulation过程,让软件自动建立do文件,并调用modelsim仿真之后,不要再关闭modelsim程序,直接在modelsim里的脚本执行窗口执行do 文件就可以启动仿真:如输入 do top_rtl_sim.do 并按回车确认。

2、 仿真过程不要关闭modelsim,修改源代码时,可以用modelsim文本编辑器,也可以使用UE等第三方文本编辑器,修改后在脚本执行窗口直接运行do文件。

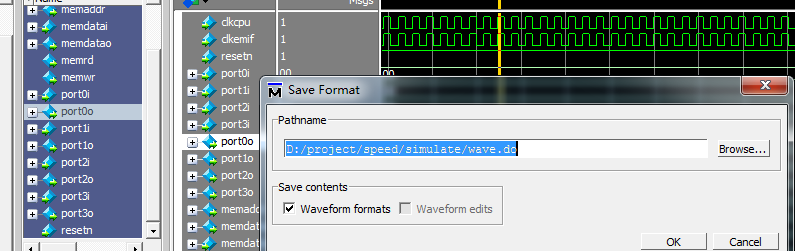

3、 为防止每次都手动修改并添加仿真信号,可以保存需要的仿真信号。在Modelsim程序的File菜单下,点击Save Format,保存信号文件为wave.do文件。

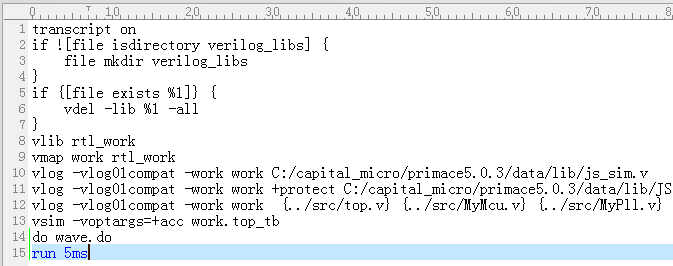

要自动添加这些信号,修改第14行为 “do wave.do”。如果再想自动执行一段时间,可以在15行添加 “run 5ms”,这样仿真停止后就可以直接观察所需要的信号了,如下图所示:

3、 直接Modelsim仿真

能不能不用Primace软件调用modelsim的方法,直接在Modelsim里仿真呢?答案是肯定的。这需要有京微雅格的仿真库文件,一旦有了仿真库文件,就可以在第三方仿真工具中灵活进行仿真。具体过程如下:

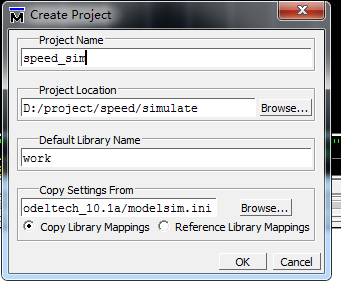

1、 建立modelsim工程,工程名:speed_sim

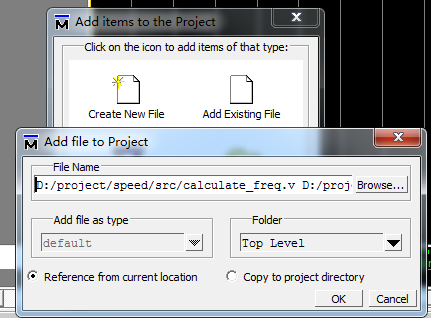

添加源文件及testbench文件:

2、 添加仿真基础库文件到工程里来

仿真库文件在安装primace的目录里:C:/capital_micro/primace5.0.3/data/lib/

3、 添加IPcore必要的源文件。例如工程里使用到FIFO,就到工程目录下的ip_core目录下找相应的源文件,也添加到工程里来。

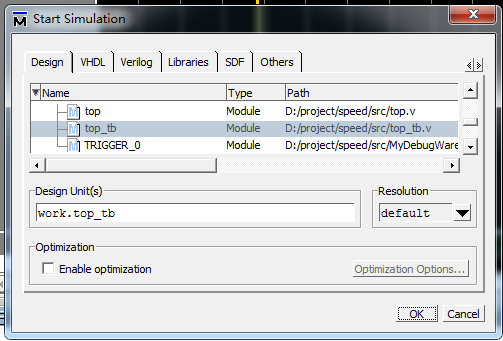

4、 编译整个工程,把必要的语法错误改掉,直到没有错误。启动仿真

使用中的简单方便的技巧:

1、 在波形文件中添加的信号,可以存为wave.do文件,需要的时候执行do wave.do就可以把所需的信号添加到波形窗口中。

2、 更新过原代码后,不需要重新启动仿真,只需要编译一下更新的源代码文件,然后点击复位按钮,把仿真器的所有状态复位,再执行设计的时间,就是新的更新后的代码仿真波形了。这样可以不用每次都通过start simulation启动仿真。

fpga相关文章:fpga是什么

评论