基于USB3.0和FPGA的多串口传输系统设计

3.1逻辑模块设计

本文引用地址:https://www.eepw.com.cn/article/265047.htm系统的逻辑模块分为时钟模块、FX3发送/接收缓存模块、发送/接收控制模块、FX3读写控制模块、485接收模块、485发送模块以及配置串口参数模块。

整个系统的数据流分为两个过程:485数据采集过程和485发送控制命令过程。

(1)485数据采集过程:485数据通过485接收模块传送给FX3接收缓存模块,在FX3数据接口没有被占用时,通过FX3读写控制模块发送给USB3.0芯片并传到PC端。

(2)485数据发送过程:USB3.0芯片通过FX3读写控制模块将数据发送到FX3发送缓存模块中,在收发控制模块检测到相关串口空闲后通过485发送模块将相关数据发送出去。

485收发相对于USB3.0速度来说,属于慢速设备。为了提高USB3.0总线利用率,此处只设计了两种缓存,即接收缓存和发送缓存,大小都设置为512KB,80路的485接收和发送buffer最终都汇聚到这两种缓存上,有效地减少了短包和空包发生率。

3.2 FX3接口时序

FPGA与FX3之间采用了Slavefifo模式,FPGA通过状态标志的flaga、flagb、flagc、flagd来判断FX3的接收/发送缓存的数据状态,当flaga/flagc为高时,表示FX3缓存中接收到了数据;当flagb/flagd为高时,表示FX3的发送缓存为非满状态,FPGA可对其进行写数据操作。

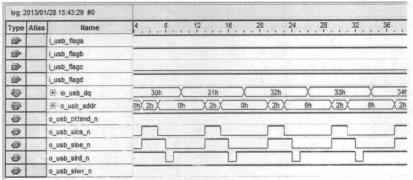

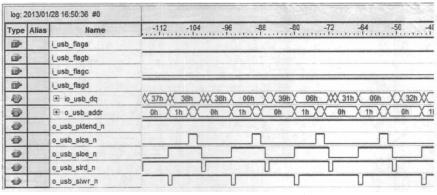

图3所示为FX3的A通道读时序,FPGA先检测i_usb_flaga是否为高电平,如果为高电平则表示A通道buffer中有数据可读,此时将通道地址信号设置为0,片选信号o_usb_slcs_n/o_usb_sloe_n拉低,o_usb_slrd_n信号拉低后,在4个时钟之后,数据将出现在io_usb_dq上,如果进行写操作则将o_usb_slwr_n拉低。对应的通道号地址选对,同时将片选信号拉低即可,写通道时序如图4所示。

图3 FX3的A通道数据读取时序

图4 FX3的B通道写数据时序

4通信速度实验结果

利用Cypress的Streamer软件,可以测试该USB3.0传输系统的传输速率。将Packets per Xfer设置为256,在win764位下(电脑配置为华硕N53XI241SN,Fresco FL1000系列的控制器)的传输速率测试结果为2.5Gb/s,满足了整个系统的性能,如图5所示。

图5读速率测试结果图

该系统适合于超高速数据的传输,具有电路简单、体积小等优点。FPGA技术与USB3.0的结合有极大的灵活性和可扩展性,基于FPGA和USB3.0的突出优点,该设计方案必将应用在更广阔的领域。

数字通信相关文章:数字通信原理

通信相关文章:通信原理

评论