Giga ADC 介绍及杂散分析(上)

当一个折叠输出信号不是在线性区域范围内时,另一个折叠输出信号恰好在线性区域内,反之亦然。这种方法可以推广到相位差更小的一组折叠信号的情况,以减小非线性区域的影响。直至,相邻折叠信号的过零点只相距一个量化单位(LSB)时,每个与折叠电路连接的比较器只需检出过零点。此时,折叠结构ADC不再要求折叠信号的线性区域范围,只要求过零点的精度。

在折叠电路设计中,一级折叠电路折叠率不宜过高,这主要是因为,如果一级折叠率过高,那么这么多输出通过长的走线连接到一起输出给下一级比较器,寄生电容对于后级的影响变得不可忽略。在TI的Giga ADC中,一般采用多级折叠电路级连的方式,例如,如果要实现一个折叠率为9的电路,采用了两级折叠级连,每级的折叠率是3,如figure10所示。

2.3.3内插电路

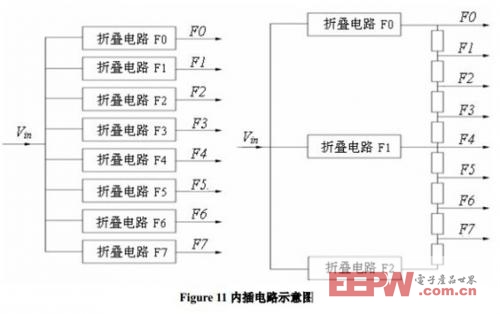

直接利用折叠电路来产生所有2N个过零点,ADC的功耗与输入电容都很大。通常的解决办法是采用折叠-内插结构,如Figure11所示。每两个折叠电路的输出之间连接一个插值电阻串,利用插值电阻的分压作用得到两个折叠电压信号之间的插值电压。每个插值节点作为输出,插值的数目称为内插率I;Figure11是当I=4的内插结果,两侧为原始的由折叠电路产生的折叠信号,夹在其间的3个信号是被节省的、由内插电路产生的折叠信号。这样,通过4倍的内插,每4个折叠信号可以节省3个折叠电路。

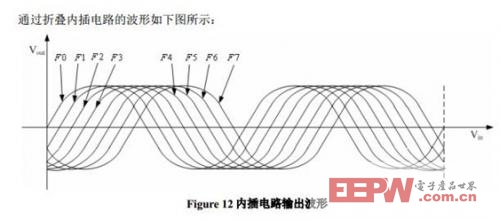

通过折叠内插电路的波形如下图所示:

2.3.4平均电路

前面提到,影响电路精度的主要误差是差分信号的偏置误差。降低差分电路的偏置误差可以增加晶体管的面积。但由于在折叠电路中,偏置误差不仅仅来自于差分电路,折叠电路中其它饱和支路的输出电流也增加了整个电路的偏置误差,简单的增加电路晶体管面积并不能有效的降低误差。由于各个放大电路的偏置误差是不相关的,这里采用了迭代的技术,使某一输出节点的偏置误差不仅仅取决于本身放大电路,还和相邻其它并行放大电路输出有关,偏置误差通过放大电路输出的迭代而随机化,降低了整个电路的偏置误差。

2.4校准电路

前面提到的各种设计电路有效的提高了ADC的线性性能和带宽,但在TI Giga ADC,仍然集成了校准电路,用以进一步优化ADC的性能。这部分校准电路包括27个高精度校准电压,采用轮询的方式依次输入到输入级的开关,并根据校准信号的输出结果通过DAC调整预放大电路的偏置电流,达到校准修正的结果。

通过Figure5可以看到,输入级的MUX开关,采保电路,输入buffer的偏置误差以及折叠电路的偏置误差等包括在校准环路里,通过校准不仅仅提高了放大电路的线性,而且提高了系统在interleave模式下两路ADC之间的一致性,改善了系统的杂散性能。

Giga ADC 介绍及杂散分析(下)

评论