2 基于FPGA的DDS信号发生器的设计

该信号发生器是作为电路板检测仪的激励信号源,产生的信号分别为:频率为16 000±0.8 Hz的正弦波,频率为128 000±* Hz,64 000±3.2 Hz,4 000±O.2 Hz的方波和周期为10μs,占空比为1:4的脉冲信号。下面以正弦波的产生为例说明DDS的实现过程。当f0=16 000 Hz,N=16时,根据式(1),则K=104。

2.1 相位累加器

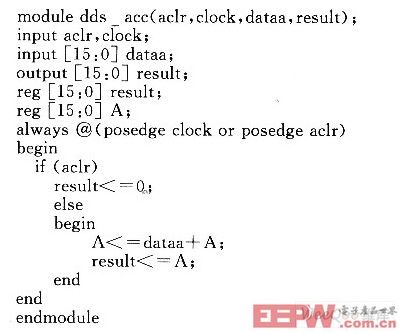

相位累加器主要是根据频率控制字生成ROM查找表的地址,采用硬件描述语言Verilog DHL实现,其源程序为:

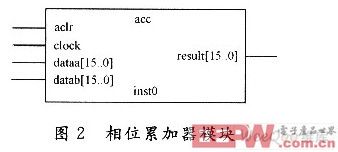

文本输入完毕后,用QuartusⅡ进行编译,然后生成.bsf文件,以便在顶层设计时调用。其生成顶层模块如图2所示。

评论