基于FPGA的高速数据采集系统设计

本文引用地址:https://www.eepw.com.cn/article/247519.htm

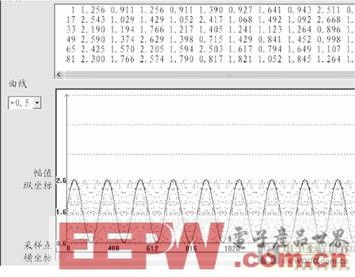

图7 仿真波形

由图7可见,从data_out这个并行的数据端口读出的数据正是在Testbench仿真测试文件中给定的那一组测试数据,仿真得到的结果是正确的。

4 数据采集系统的实验

在FPGA控制A/D芯片接口的软件设计中,是通过FPGA内部的逻辑电路实现了分频,并将分频后的信号作为A/D芯片工作的采样时钟,经过测试,得知A/D芯片的采样频率为1.08 MHz,通过信号发生器,将输入的模拟信号设为10 kHz、幅度为3 V的正弦波,采样转换后的数据上传到上位机中,显示的波形如图8所示。

图8 10KHZ信号输入时得到的波形

在同等条件下,把输入的模拟信号的频率调整为5 kHz。A/D芯片的采样频率仍然为1.08 MHz。得到的显示波形如图9所示。

图9 5 kHz信号输入时得到的波形

由图8和图9可知,在对模拟信号采样时,当采样率不变时,输入模拟信号的频率越低,相对地就提高了采样点、减小了采样间隔,在图形中就越能体现出原始模拟信号的信息,得到的波形就更加的理想。

5 结束语

本文在研究了FPGA和USB2.0技术的基础上,提出了数据采集系统的总体设计方案,以FPGA和USB2.0为技术核心,设计了硬件电路和软件代码并在ModelSim环境下通过了仿真测试。该系统不仅能够实现一般用途的数据采集,还实现了系统的高速化、集成化和低功耗工作,为便携化数据采集系统提供了一种设计思路。

锁相环相关文章:锁相环原理

评论