基于C6000系列DSP的MPEG-4编码器实现

3.2 利用VLIW结构设计程序

利用VLIW结构设计程序可以充分利用DSP多个功能单元并行工作的特性。DSP的每一个通道都有四个功能单元(L、S、M、D),每个功能单元负责完成一定的逻辑或者算术运算,另外A、B两个通道的互访可以通过交叉单元1x、2x完成。程序2中,在一个时钟周期内并行执行八条指令,使用了所有的功能单元S2、S1、L1、M2、L2、M1、D1、D2,同时使用了所有的交叉单元1x、2x,已经达到极限。但是这种并行指令的使用也有一定的限制,其最根本的要求就是不能引起资源冲突,例如:

·不能用同一个功能单元;

·不能对同一通道的寄存器进行两次long型写操作;

·不能对同一通道的寄存器同时进行long型读操作和存储操作;

·读同一寄存器不能超过4次;

·在同一个时钟周期不能有两个指令写入同一寄存器,这不是说向同一寄存器写的两条指令不能放在同一个并行指令包内,而是说两个指令不能在写寄存器的那个时钟周期并存。

仍然以MPEG-4中的DCT算法为例说明VLIW结构在程序优化中的作用。进行DCT变换的原始数据是short型的,因此可以将两个数据合成一个32位的数据来访问;为了使两个通道并行访问数据和运算,应尽量把要访问的数据平均地分配给不同的通道寄存器;并且通过交叉单元使两个通道相互访问,从而达到很高的并行性,大大提高了编码效率。

MPEG-4编码的其它算法,例如逆DCT、运动估计、运动补偿等算法都包含着大量的循环运算和数据访问。因此利用DSP的VLIW结构和流水线结构优化MPEG-4编码算法就成为一种非常合适的方法。

当然,编写程序时不是将DSP的VLIW结构和流水线结构分开考虑,而是将两者结合起来,在编写每一条指令时都要清楚这条指令的执行周期以及使用的功能单元,这样才能编写出高效的程序。

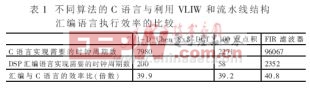

表1对1-D Chen 8×8 DCT、100点点积和FIR滤波器算法的C语言实现与利用VLIW及流水线结构的汇编代码实现进行比较。从统计数据可以看出,利用DSP结构编写的汇编代码执行效率要比C语言编写的代码执行效率高40倍左右。因此充分利用DSP的VLIW结构和流水线结构设计汇编程序能够使效率大幅度提高。

本文对MPEG-4编码卡进行了设计,主要难点是MPEG-4编码算法的优化,MPEG-4的编码复杂、代码量大。利用C6000系列DSP的VLIW结构和流水线结构设计出了MPEG-4编码算法。实验证明,算法效率得到了大幅度提高。

评论