基于C6000系列DSP的MPEG-4编码器实现

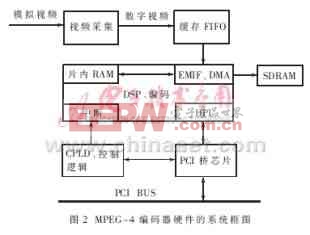

2 MPEG-4编码卡的硬件设计

2.1 视频采集

视频采集部分主要完成模拟视频到数字视频的转换,包括一片视频采集芯片和一片小的CPLD。CPLD的作用是控制视频采集芯片,将采得的数据从8位或16位转化为32位,并且使数据按照Y、U、V分开的方式排列。这样相当于对采集到的数据进行了一次预处理,以便于视频编码使用。另外,CPLD将32位宽的数据输出给32位的FIFO。用32位的FIFO以及将视频数据转换为32位,可以使DSP读取视频数据时32位的数据总线没有空闲,从而提高DSP读取视频数据的效率;这里使用FIFO是为了减少DSP读取数据的时间、降低高速设备和低速设备的不匹配。每次FIFO半满时,CPLD会给DSP发送中断信号,并且在中断处理程序中使用DMA方式读取视频数据;如果不使用FIFO,DSP会频繁中断,从而花费大量时间在入栈、出栈以及寄存器的设置上。

2.2 视频编码

DSP读入视频数据后进行先期处理,如将YUV格式转为RGB格式等;然后进行MPEG-4视频编码。在这一过程中,数据访问通常要占用50%的时间,算术运算要占用30%的时间,控制要占用20%的时间。因为需要进行运动估计和运动补偿,在数据存储器中通常保存一帧I(原始帧)帧图像和至少一帧P(预测帧)帧图像,这些图像占用的空间都比较大,因此一般都放在外部存储器SDRAM里。在编码过程中还要存储DCT系数、运动向量、量化矩阵、可变长编码表、Z形编码表等,由于占用较小的存储空间而且会反复用到,因此把它们放在片内存储器中。

评论