基于DSP/FPGA的超高速跳频系统基带设计

最上方信号是发射端跳频序列的波形;中间信号是接收端跳频序列的波形;最下方是帧同步信号。当识别到巴克码时,帧同步信号出现一负脉冲,完成接收端调频序列发生器反馈系数和初始相位的加载。从图9中可知:(1)接收端跳频序列与发射端跳频序列变化规律一致,跳频图案同步成功;(2)最小码距满足要求,通过对偶频带法得到宽间隔跳频序列成功。

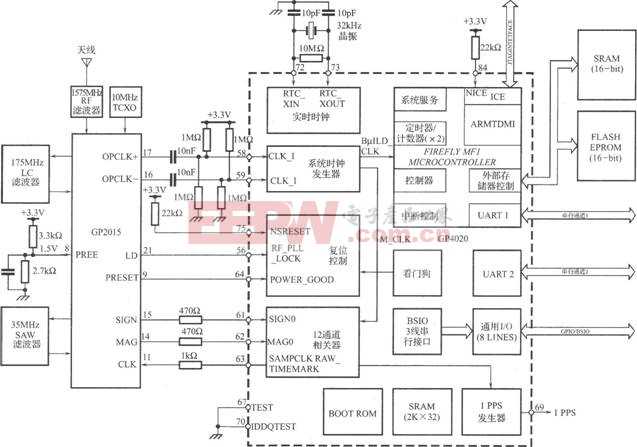

系统以TI公司DSP为中心控制单元,Altera公司的FPGA为硬件逻辑平台,AD公司的DDS为频率合成器,采用2FSK调制解调方式,超前滞后支路的位同步方式,TOD跳频图案同步方式,以m序列作为跳频序列,辅助对偶跳频间隔控制手段,实现了高速、宽间隔跳频通信系统。系统达到40kbps的跳频速度,1 024个跳频频道,108M~189.84MHz的跳频带宽,400kHz的最小跳频间隔,小于0.5s的入网时间以及小于30s的同步最大时差。

本高速跳频通信系统与同类系统相比最大的优势体现在它40kbps的超高速跳频速率和近百兆的跳频带宽上。通过与国内外类似系统进行比较,40kbps的跳频速率处于技术领先位置。各关键模块性能优良,接口一致且工作稳定,可以灵活组合成多种数字通信系统的基带部分。相信本文对今后数字通信系统基带部分的研究和实现具有很强的借鉴意义。

参考文献

1 梅文华. 跳频通信.北京:国防工业出版社,2005

2 夏宇闻.Verilog数字系统设计教程.北京:北京航空航天大学出版社,2003(第1版)

3 Uwe Meyer-Baese著,刘 凌,胡永生译.数字信号处理的FPGA实现.北京:清华大学出版社,2003(第1版)

4 梅文华,张志刚.一类新的宽间隔跳频序列族的构造[J].电波科学学报,2002;17(1):16~20

5 张申如,梅文华,王庭昌.计数式TOD跳频码发生器算法的构造.电子与信息学报,2002;24(8):1096~1101

6 TI.TMS320C5000 Assembly Language Tools User′s Guide[M].2002

7 TI.TMS320C5000 Chip Support Library API Reference Guide[M].2002

8 Altera. Cyclone Datasheet[M].2004

评论