一种新型告诉浮点多DSP并行处理系统结构

利用软件无线电的原理,可以构建通用的硬件平台,辅之以必要的软件系统,能实现各种信号处理功能。

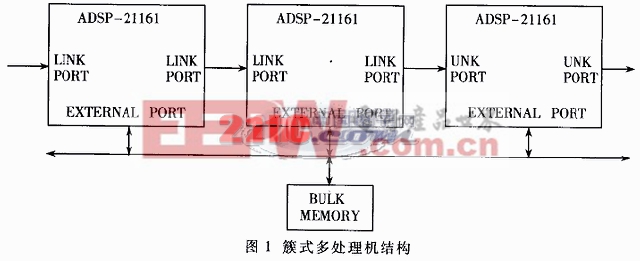

实时信号处理要求巨大的计算量与超高速的计算速度,而现在的单片DSP很难满足要求,因此必须采用合理的多DSP并行计算结构。雷达信号处理的特点要求处理结点具有大的I/O带宽,以实现高数据吞吐能力,通用的系统还必须支持多种算法,因此应能根据不同并行算法的要求灵活地改变多DSP并行计算的拓扑结构,并提供方便多样的相互通信手段。

1 ADSP-21161N芯片简介

大容量内部双端口SRAM,容量可达到1Mbit,分成两个存储区,一个周期可同时完成指令代码及操作数的存取,并可任意设置成16位、32位或48位字宽,给不同的应用带一籽方便。

两套双向高速LINK数据传输,每套LINK口受独立的DMA控制 器、发送/接收数据FIFO的支持,可进行最高达100MB/s的高速数据传,大大提高了并行处理能力,可借以构成松耦合的分布式并行系统。

另外,还有SPI接口、可编程I/O管脚(FLAG)以及同步串口等通信端口。

相关推荐

-

-

-

fancy_wind | 2004-10-29

-

电子阳光 | 2004-11-04

-

-

-

wuren_13 | 2004-11-08

-

wuren_13 | 2004-11-08

-

-

ping1125 | 2005-03-03

评论