FPGA与外部存储设备的接口实现

DRAM性能简介

DRAM与SRAM不同,它只能将数据保持很短的时间。为了保持数据,DRAM 必须隔一段时间刷新一次,如果存储单元没有刷新,数据就会丢失。SRAM虽不需刷新,但断电后会丢失数据。SRAM的数据传输速率从10 ns到30 ns不等,DRAM要比它慢30 ns左右。因此,SRAM通常用于高速缓冲存储器,而DRAM通常用来存储较大的数据。HY57V281620HC(L/S)T是4Banks 2M 16bit的同步动态存储器,性能特点包括:

1.工作在3.3 0.3V电压下;

2.所有器件管脚都与LVTTL接口兼容;

3.所有的输入和输出操作都是在时钟CLK上升沿的作用下进行;

4.通过UDQM或者LDQM来实现数据延时功能;

5.内部有四个bank可以进行操作;

6.自刷新功能,刷新周期为4096;

7.可编程的猝发类型、猝发长度;

8.可编程的的CAS延迟为2或3个时钟周期。

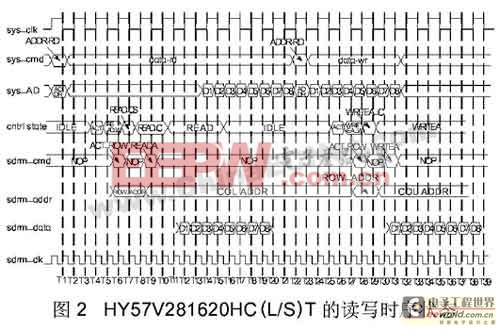

由上面的特性可知,DARM的读写操作与SRAM有较大的不同。根据HY57V281620HC(L/S)T的读写状态的时序要求,其读写时序状态如图2所示:

|

设计实现

当设计FPGA与SRAM的接口时,由于它的传输速度较快,所以只需着重考虑如何保证存储数据的正确性,而不需要考虑用其它方式来提高SRAM的存储速度。本设计的做法是一次性写满128k数据后,再一次性读出128k数据。为了保证数据的正确性,要求在写数据时不能读数据,而在读数据时不能写数据。

当设计FPGA与DRAM的接口时,为了能满足各种系统的使用要求,本设计创建了时钟频率、猝发长度、延时节拍等可编程参数。在具体操作DRAM时,首先,必须进行初始化配置,即写模式寄存器,以便确定DRAM列选延迟节拍数、猝发类型、猝发长度等工作模式。然后通过ACT命令激活对应地址的组,同时输入行地址。最后,通过RD或WR命令输入列地址,将相应数据读出或写入到对应的地址。操作完成后,用相关命令中止读或写操作。在没有操作的时候,每64ms必须对所有存储单元刷新一遍,防止数据丢失。

下面本文将指出在设计实现中需要特别注意的几个问题,并给出了相应的解决方法 。

首先,是如何控制SRAM的读写功能。这就需要与IS63LV1024读写时序要求和真值表的描述相配合。本设计为了避免连读或连写数据时出错,考虑了一种通过读写数据请求的方法来尽量避免读或写数据出错的可能。即每写完或读完一个数据后都要先进行请求,然后才能继续读或写数据。ASRAM的状态转移图如图3所示:

下面给出了图3中各个状态所表示的意思:

DOREAD表示读数据的请求;

DOWRITE表示写数据的请求;

STIDLE表示存储器处于空闲状态;

STWRITE1表示存储器处于写准备状态,准备写数据;

STWRITE2表示存储器处于写状态,开始写数据;

STREAD1表示存储器处于读准备状态,准备读数据;

STREAD2表示存储器处于读状态,开始读数据。

只有当系统时钟的上升沿到来时,才会触发这个状态机改变一次当前状态。

刚开始时,存储器的初始状态为空闲状态,当有请求来时才判断是读或写请求,如果没有请求就一直保持空闲状态。虚线表示自动按顺序进入下一个状态。

评论