基于SDI接口的实时图像增强显示系统

经黑白相机输入的图像数据经过协议转换处理后得到的是SDI接口视频YCbCr格式中亮度Y分量,这时将CbCr在程序里填充80h,就构成YebCr信号,而后用于输出显示,为了增强显示效果,颜色更加能丰富人眼的视觉效果,下面给出一个算法将灰度转换为伪彩色。

实现伪彩处理,通常是把当前像素灰度值作为存储地址查找RGB伪彩码表,将码表中对应的RGB三色值用RGB转换到YebCr彩色区间,而后输出伪彩图像。在FPGA里实现的基本方法是最大限度地利用FPGA的IP核,将RGB码表写到FPGA的内嵌RAM核里,在程序中依次遍历查找表和计算下面的公式计算出相应的CbCr值并且输出。

R=1.164(Y-16)+1.596(Cr-128)

G=1.164(Y-16)-0.813(Cr-128)-0.391(Cb-128)

B=1.164(Y-16)+2.018(Cb-128)

2.3 画幅缩放

图像的画幅缩放也被称为图像重采样,它是视频处理中的一项重要技术。在SDI显示输出模块中,由于标清SDI显示画幅分辨率是720× 576,前端输入CameraLink或者其他接口的图像分辨率随机,所以必然会用到图像画幅缩放,否则,如果图像分辨率超出SDI的这个范围,就会导致显示不全,如果分辨率小于这个范围,就会导致有黑框,直接影响后续的显示效果。

目前画幅缩放的算法种类繁多,但基本方法都是插值运算方面的算法,例如最近邻插值、双线性插值以及立方卷积插值算法等,但最近邻插值算法在亮度变化比较快的图像边缘比较粗糙;立方卷积插值算法非常复杂而且运算量大,不满足实时处理条件。同前面2种插值算法比较,双线性插值算法运算量少、实时性高,适合于在FPGA内部实现。

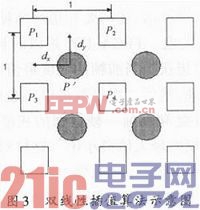

如图3所示,假设原始图像中的某点(x,y),则相邻的右侧和下方像素点位置为(x+1,y),(x,y+1),(x+1,y+1),假设它们的灰度值分别是P1,P2,P3,P4,在水平方向和垂直方向上的位移都是单位1,并假设待插入点的位置坐标为:(x+dx,y+dy)。

那么根据双线性插值算法原理得到插入点的灰度值为:

P’(x+dx,y+dy)=(1-dx)(1-dy)P1+dx(1-dy)P2+dy(1-dx)P3+dxdyP4

化简后得到:

P’(x+dx,y+dy)=P1+(P2-P1)dx+(P3-P1)dy+[(P4-P3)-(P2-P1)]dxdy

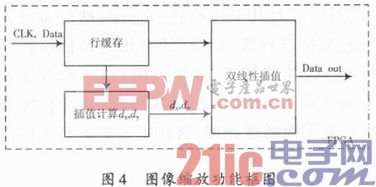

从上式看出,当知道待插值点的偏移距离dx和dy后,那么该插值像素点的灰度值可根据周围的4点得到。该系统中的画幅缩放处理正是采用双线性插值算法,其在FPGA内部实现的具体功能如框图4所示,主要由数据缓存单元、双线性插值单元、插值系数控制单元组成。

在实现图像缩放算法以前,首要算出图像的缩放因子k。这里以一行图像为例,以单位长度“1”表示相邻2个像素的距离,图像缩放前的分辨率为A×1,图像缩放后的分辨率为B×1,则缩放前后的图像的像素缩放因子k=B/A。例如,分辨率为640x512的图像缩放为720x576的图像,则在水平方向上缩放因子k=1.25;垂直方向上的缩放因子k=1.125;根据不同的情况,在水平、垂直方向上的缩放比例因子不同。

根据图4和插值的运算公式,每经过一个像素时钟,插值系数dx,dy需要实时提供给插值运算模块,这就要求FPGA时序同步,并且FPGA各个功能模块能够有效配合。

3 实验结果及分析

将硬件系统和相机连接,该相机基本参数是320x256分辨率,14 b像素深度,帧频25/50可调。通过PC机的RS 232串口连接转一个转换设备,使之满足RS 422差分协议,以便发送命令给硬件系统和返回硬件系统状态。

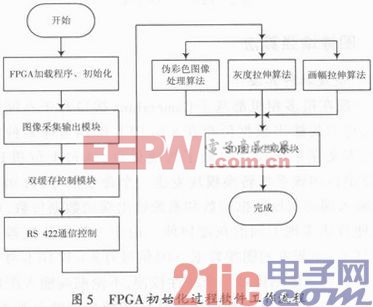

FPGA程序采用模块化方式,分为图像采集输出模块、双缓存控制模块、通信控制模块、伪彩处理模块、灰度拉伸模块、画幅缩放模块和SDI时序生成模块,其中伪彩处理模块、灰度拉伸模块和画幅缩放模块通过RS 422接口发送不同的指令给FPGA,就会触发相应的模块工作,具体FPGA初始化过程中软件工作流程如图5所示。

评论