基于FPGA的IPV6数字包的拆装实现

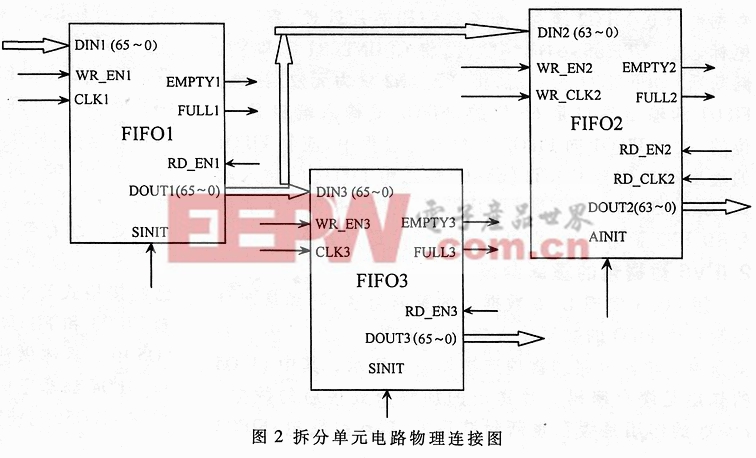

图中的三个FIFO都是由Xilinx公司的开发工具ISE6.1自带的Core IP生成的。其中FIFO1和FIFO3是同步FIFO,工作时钟为频率62.5MHz,输入输出数据宽度都是66bit;FIFO2是异步FIFO,输入时钟频率为62.5MHz,输出时钟频率为50MHz(密码芯片的工作时钟频率为50MHz),输入输出数据宽度都是64bit。

FIFO1的输入数据为IPV6数据包。可以看出,该数据是以并行的66bit信号传输的,即每一时钟周期并行传送66bit数据,其中每个周期的高两位(即65位和64位)为数据包的头尾标志,这是IPV6路由器内部根据实际处理需要加上的,“10”表示一个完整数据包的第一周期,“11”表示数据包的中间内容,“01”表示一个完整数据包的最后一个周期。因为IPV6数据包的包头是固定长度的,为40字节(等于5×64bit),故数据的前五个周期为IPV6数据包的包头,包头后面跟的就是数据包的数据部分。

下面讨论IPV6数据包的包头和数据部分的拆分过程。

首先判断FIFO1输入端数据的头尾标志DATA(65~64)与FIFO1的满标志FULL1,如果DATA(65~64)=“10”且FULL1=“0”,即判断到一个完整数据包的开始且FIFO1未满,则使FIFO1的写使能WR_EN1有效,写入数据;如果DATA(65~64)=“01”,好判断到一个完整数据包结束时,则使WR_EN1无效,这样一个完整的数据包就缓存到了FIFO1时。

当判断到FIFO1的空标示EMPTY1=“0”,即FIFO1非空间,令FIFO1的读使能信号RD_EN1有效,将FIFO1中的数据读出,直到EMPTY1=“1”,即FIFO1空为止。对读出的数据设定一计数器COUNTER1进行计数,当DONT1不为0即FIFO1输出端有信号时开始计数。当0COUNTER1=5时,令FIFO3的写使能信号WR_EN3有效,将数据包的包头写FIFO3缓存;当COUNTER1>5时,令WR_EN3无效,WR_EN2有效,将IPV6数据包的数据部分送FIFO2缓存,准备送密码芯片处理,直到头尾标志DOUT1(65~64)=“01”时,将COUNTER1清零,在判断到COUNTER1为0后,将WR_EN2置为无效。注意:FIFO1的输出端口是66位,FIFO2的输入端口是64位的,故在FIFO1向FIFO2写数据的过程中,应将FIFO1的输出端口信号DOUT(63~0)传送给FIFO2的输入端口DIN2(63~-)。当判断到FIFO2非空间,将其读使能信号RD_EN2置为有效,即可向密码芯片送出数据。

相关推荐

-

-

-

-

xiaohua | 2002-09-24

-

sandman555 | 2005-02-05

-

-

herbertwj | 2004-08-15

-

-

-

-

-

-

sandman555 | 2005-02-05

-

sandman555 | 2005-02-05

评论