对基于FPGA的作战系统时统的研究与设计

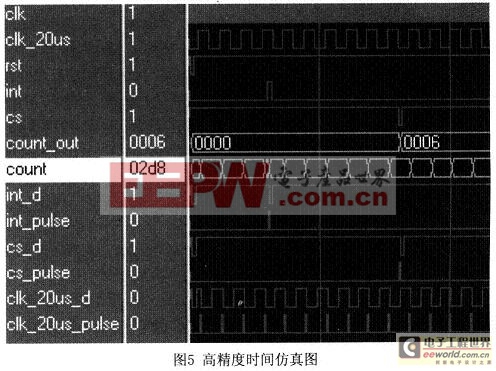

其中clk(时钟)、clk_20μs(20μs周期时钟)、rst(复位)、int(外部信号)、cs(锁存当前计数值)为输入信号。count_out为输出的16位二进制计数值(eount out[15..0])。本功能能够给出20μs精度的计数,在秒脉冲到来时(上升沿)产生中断,同时启动计数器,为20μs一次的计数,最大计数值为50000。计数值存入寄存器,可随时读取当前计数值,得出计数值后可换算成ms等其它值。其仿真结果如图5所示。

5 结束语

利用FPGA完成了作战系统对时统模块功能要求的设计,经在工程项目中使用验证,其功能完全满足要求。设计中使用的FPGA(EPM7256SRl208一lO)是一种高性能的CMOS EEPROM器件,通过4个引脚的JTAG接口能够进行在线编程,在开发过程中实现了快速有效的重复编程。借助其可重复编程使用的灵活性,通过改写FPGA内部逻辑来实现不同的功能需求,避免了硬件的重复设计,缩短了设计周期,适应了发展的需要。

评论