一种基于FPGA/DSP的灵巧干扰平台设计与实现

该平台采用CPCI结构,主要由A/D,D/A转换及DDC,DUC模块、DSP信号处理模块、CPCI总线接口、FPGA高速数字传输、存储器、PCI桥模块、CPLD模块等几部分组成。主要特性如下:

(1)单通道14 b分辨率,150 MSPS采样率的高速带宽ADC AD9254。

(2)宽带数字正交下变频DDC芯片AD6636,支持抽取与滤波。

(3)单通道14 b分辨率,300 MSPS采样率的高速宽带

(4)宽带数字正交上下变频DUC芯片GC5016,支持抽取与滤波。

(5)处理器之间(包括两片TMS320C6713 DSP芯片与一片Xilinx Virtex 4 FPGA芯片)实现了多种灵活的高速实时数据传输与交换通道。

(6)CPCI总线兼容PCI 2.2 64位/66 MHz,支持Master(DMA)/Target burst模式。

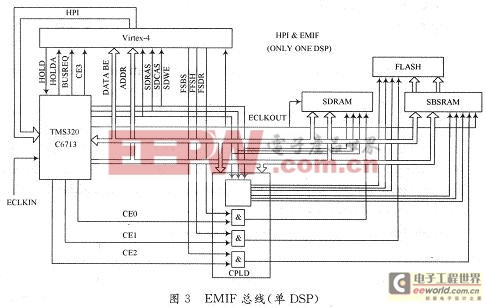

FPGA和DSP协同完成信号处理功能,这里重点说明其协同原理(见图3)。

FPGA与DSP主要通过共享EMIF总线上的存储空间进行数据交换。存储器包括:共128 MB的SDRAM,512 KB的SBSRAM,8 MB的非易失FLASH,它将大大提高数字信号的传输与处理速度。DSP外部总线EMIF各种存储器及设备资源分配如下:CE0(SDRAM),CE1 (FLASH),CE2(SRAM),CE3(FPGA)。资源分配由FPGA和DSP依靠申请总线决定,因此可以通过重新编程加以修改。对于C671 3来说,EMIF总线为32位,时钟最高为100 MHz,因此总线的数据吞吐率最高为400 MB/s。为了提高总线效率,设计中FPGA与DSP都可以独立访问:EMIF总线上的存储空间,但不能同时访问。FPGA作为EMIF总线设备之一,与 SDRAM,SB-SRAM共享数据与地址总线。同时,FPGA也是EMIF总线主设备之一,与DSP共同管理EMIF总线。也就是说,FPGA也可以主动发起访问SDRAM,SBSRAM。因此,FPGA与DSP共享EMIF总线上所有的存储空间。在默认状态下,由DSP管理EMIF总线。FPGA通过使能HOLD控制线向DSP申请总线,DSP在处理完当前任务后,响应请求,以HOLDA控制线使能作为回应,并将自己所有EMIF管脚置为高阻。这时, FP-GA就可以接管EMIF总线,进行相应的操作。FPGA与DSP进行数据交换的另一种方式是通过HPI(主机口)。TM$320C6713的HPI 是一个16 b宽的并行端口。FPGA作为HPI主设备与DSP的HPI相连,掌管着该端口的主控权,通过HPI直接访问TMS320(26713的存储空间和外围设备。

2.2 平台软件设计

本设计中,FPGA不仅需要与

基于FPGA的控制软件主要完成以下功能:

(1)程序加载

程序加载分为FPGA的程序加载和DSP的程序加载。FPGA的程序加载是指通过PCI总线来给FPGA加载程序。其加载路径为:上位机→PCI总线 →FP-GA。DSP的程序加载是指通过HPI来给DSP加载信号处理程序。其加载路径为:上位机→PCI总线→FP-GA→HPI口→DSP。

(2)

此过程是指FPGA把ADC(DDC)数据采集并保存在外部存储器(SDRAM或SRAM)中以备FPGA和DSP处理的过程。其数据流路径为:外部数据源→ADC→DDC(只进行ADC时DDC省略)→FPGA→SDRAM或SRAM。

(3)数据的DMA操作

DMA用于实现上位机对外部存储器(SDRAM或SRAM)的数据读写功能。DMA读的数据流路径是:外部存储器→FPGA→DMA→上位机→二进制文件。DMA发的数据流路径是:上位机→DMA→FPGA→SDRAM。

(4)配置DDC和DUC

此过程是把DDC和DUC配置文件通过FPGA配置到AD6636和GC5016中。其配置路径为:上位机→PCI总线→FPGA→DDC或DUC。

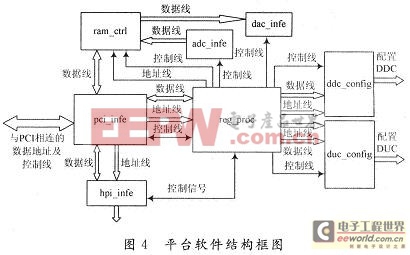

软件设计采用Verilog硬件描述语言和模块化设计,结构如图4所示。

图4中,reg_proc模块是软件控制的核心部分。通过定义内部寄存器接收上位机的控制字,给各模块发出控制信息;pci_infe是FPGA与PCI 总线的接口模块,实现平台与上位机的信号交互;FPGA通过HPI口对DSP的程序加载,由hpi_infe模块实现;adc_infe和

评论