利用Virtex-5LXT应对串行背板接口设计挑战

IP核

大多数串行背板应用依然采用专有协议。然而,最近的一些新设计已开始采用XAUI和GbE等标准化协议。这主要是因为一方面这些标准日益成熟,另一方面基于这些协议的交换结构专用标准产品(ASSP)也不断涌现。利用ASSP实现交换应用可以大大缩短开发周期,但是设计人员发现,必须通过提供增值功能(主要是在线卡上)来实现产品差异化。

由于这些串行收发器是专为支持大多数串行背板标准协议而设计的,因此FPGA是实现定制特性的理想平台。串行收发器和交换接口一起允许实现符合标准的设计,并具有增值功能,而所有这些都是在单个芯片器件上实现的。

为了帮助缩短设计周期,Xilinx推出了面向XAUI、GbE、SRIO和PCIe等主要串行I/O接口标准的模块化IP核。为了确保互操作性,这些IP核经过了一系列兼容性测试和独立的第三方验证。为了有助于产生“轻量级”串行协议设计,Xilinx还推出了Aurora协议―它特别适用于要求最大限度地降低开销、优化芯片资源利用率的比较简单的设计。

由于以太网和PCIe技术的应用范围越来越广,Virtex-5LXTFPGA也实现了嵌入式三态以太网MAC和PCIe端点模块。这些特性能够帮助节省大量FPGA资源,例如那些需要在控制板应用中实现接口的客户。

目前,即使一些比较新的系统仍在使用并行接口芯片,因此,Xilinx也推出了适用于诸如SPI-4.2、SPI-3和PCI等常见并行接口的IP核,以便快速设计串行到并行桥,满足许多应用的需求。

除了串行和并行接口IP核,Xilinx还提供了更加完善的IP解决方案,以进一步缩短产品开发周期和上市时间。包括用于优化背板流量的流量管理器和允许板卡之间实现“多对多”连接功能的网状结构参考设计。此外,ChipScope Pro串行I/O工具套件可以帮助设计人员快速设置和调试串行收发器,以及进行BERT测试。

应用示例

下面,举例说明如何集成所有这些解决方案元件,打造一个适用于星形系统和网状系统的完善的串行背板结构接口FPGA。

1. 星形背板拓扑应用

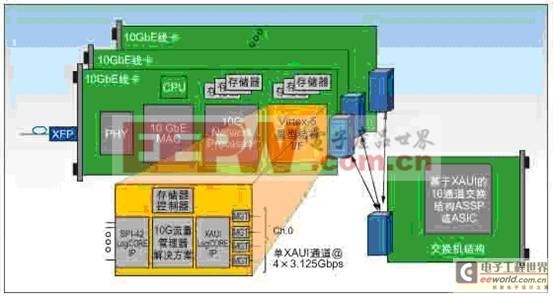

星形背板拓扑十分经济,尤其是在包含大量板卡的系统中,因此,大量高端基础设备采用星形拓扑。图1所示为实现了基于FPGA的星形交换接口的10GbE线卡示例。该FPGA例示了一个XAUI LogiCORE IP核,并利用4个串行收发器连接至16通道XAUI交换结构卡。此外,该FPGA还具备一个LogiCORESPI-4.2核,以连接至10Gbps网络处理单元。

图1:10GbE线卡中的星形结构I/FFPGA。

在串行接口和并行接口之间的是流量管理器IP解决方案,它负责对传入和传出的信息流执行服务质量(QoS)相关功能。存储器控制器负责控制主要用作数据包缓冲器的外部存储器。这种结构的优越性包括:提高了SerDes和逻辑电路功能的集成度、借助IP解决方案加快了产品上市时间、同时实现客户特定系统技术规范。还可提供不错的信号完整性和很低的SerDes功耗(总功耗仅为400mW左右)等。客户可以在XC5VLX50T器件上实现这一切。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论