Spartan-3实现DSP嵌入系统在FPD中的应用

Spartan-3设备以最低成本提供高密度的FPGA,这使得它们非常适合于数量大、注重成本、以DSP为核心的应用程序。

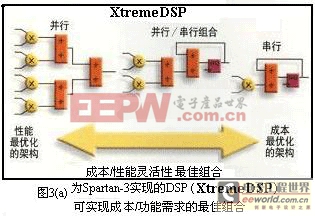

其嵌入式18×18乘法器(最多104个)、每秒最多3300亿次乘法和累加运算(MAC/s)、优秀的高速DSP功能的并行实现能力、灵活的串联架构,可实现成本/功能需求的最佳组合,见图3(a)所示最大的DSP成本/性能灵活性。

预验证的DSP算法和核心,即滤波器、检波、变换、算法、FEC、相关器。而Spartan-3 FPGA 在高性能DSP应用中,有各种不同FIR滤波器技术的适用情况,而FIR滤波器的算法为:

公式中n个系数与n个相应的数据采样相乘,再对内积求和产生单个结果。系数数值将确定滤波器的低通/高通/带通特性,可以利用不同的架构和不同的方法来实现滤波器的功能。

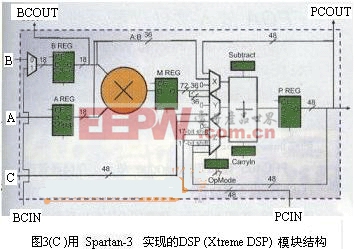

由此可以说,因为FPGA是极高并行度的信号处理引擎,能够满足算法复杂度不断增加的应用要求,通过并行方式提供极高性能的信号处理能力。Xilinx的XtremeDSP模块,如图3(b)所示,使得Sparten3系列FPGA可以为高性能的数字信号处理提供理想的解决方案,达到传统上由ASIC或ASSP完成的高性能信号处理能力。可以针对数字通信和视频图象处理等应用开发高性能的DSP引擎,也可在可编程DSP系统中作为预处理器或协处理器等。

由于嵌入式18×18乘法器(最多104个)适应DSP应用中的众多的功能。提高了操作数输入、中间积和累加器输出的可编程流水线操作。

在复杂算法的数字处理系统中,系统要求的不断提高和集成规模的不断扩大,使得系统结构在设计的开始阶段是不明确的,不可能直接用RTL(寄存器转移级)设计方法进行描述,所以将系统集成到数字芯片中。

采用数字技术对复杂算法进行硬件实现时,首先遇到的问题是在结构上并没有预先的规定,因此需要首先对算法建模和仿真进行优化。与基于RTL针对结构清晰的设计方法不同,算法设计把焦点从针对结构的细节转移到对设计的整体要求和行为,在最高的算法层次上考虑如何进行设计,对系统的行为描述定义了设计要执行的算法,不涉及或很少涉及实现细节,因此行为描述比RTL描述要简洁的多。

图3(c)为易用的DSP设计流程所示, 糸统产生器的DSP设计环境,包含了系统数学建模、算法优化和改进、设计校验和诊断及HDL产生和仿真等。而综合DSP设计服务包括DSP设计等级、现埸工程服务。

评论