基于FPGA的仿真系统数据采集控制器IP核设计

3 系统实现

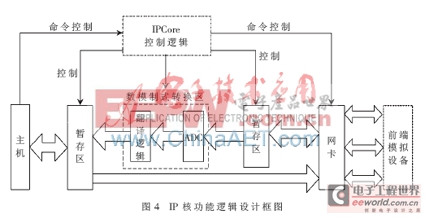

本IP 核功能逻辑的设计基于其任务逻辑定制的基本功能和技术指标。本设计的任务逻辑主要完成对模拟仿真系统前端模拟设备发送指令以及采集前端模拟设备状态量数据。其功能逻辑也基于发送指令和接收数据两个数据流来设计,如图4所示。

为避免高速、高频系统时序中常存在的竞争、毛刺危险以及建立与保持时间相抵触等问题,本IP核采用同步设计的方案。同时,为解决实际中仍会经常出现系统产生毛刺和时钟偏斜等问题。本IP核中拟将时钟控制改为触发器输入允许,将时钟选择改为独立的时钟分析[7]。

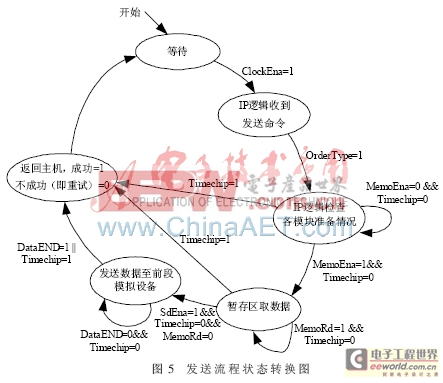

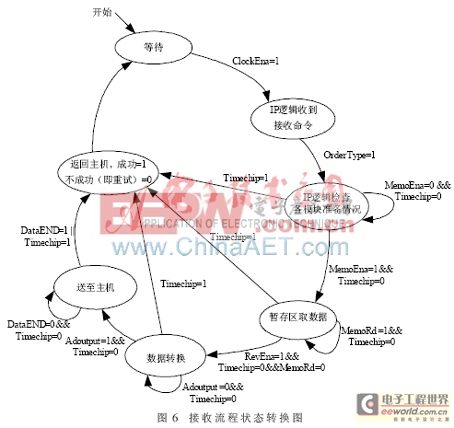

为加快本设计的运行速度及处理效率,本IP核的设计以功能逻辑处理机制为基础,分别对发送流程和接收流程设计状态机并实现[8]。

在发送流程的状态转换过程中,共有6个状态,如图5所示。IP核的控制逻辑判断来自主机的发送数据命令后,首先检查其各功能模块的准备情况,如果准备好,即开始发送数据,从寄存器单元中取出待发送数据并送至网络通信模块,由其发送至前端模拟设备。在此过程中,不断检测发送完成标志位DataEND,如果该标志位变为有效则表示发送成功,将此信息反馈给主机并进入下一工作周期等待状态;如果超时该标志位仍未变化,则反馈回主机发送失败的信息,并请求重发。

相应地,如图6所示,接收流程的状态转换过程有7个状态。其工作大致与发送流程相同,只是接收数据从寄存器单元读出后,要先经过数据模式的转换后,再发送给主机使用。

评论