一种基于CPLD的声发射信号传输系统设计

3 cpld逻辑控制

本系统中由于要对高速信号进行处理,因此,对控制信号的时序要求比较严格。在控制芯片的选择上要尽量选用时延小、速度快的芯片。本设计采用美国altera公司的max7000s系列可编程逻辑器件epm7128slc84-15,并采用max+plusⅱ来完成系统的输入、编译、验证及编程,进而完成向量测试及仿真.最后的数据可通过下载线传输到芯片中来完成芯片的配置。

3.1 cpld逻辑控制电路

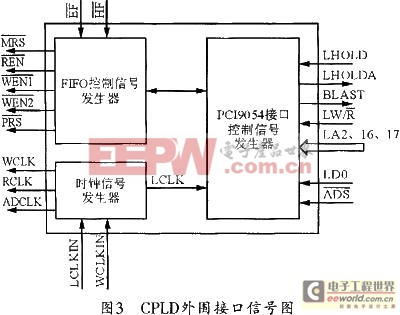

cpld为采样控制器的核心,数据传输所要求的严格时序控制关系就由cpld负责处理。它在本系统中主要负责产生与pci9054的握手信号、数据存储器的片选信号和读写控制信号。cpld的外围信号接口如图3所示。

cpld可根据fifo存储器的时序控制要求产生控制信号,并在第一个时钟周期中将数据分别存入fifo和数据锁存器74ls373中,而在第二个时钟周期将锁存器中的数据再存入fifo,从而完成并行数据向串行数据的转换。同时根据存储器的相关信号向pci9054控制器发出中断请求,并在pci9054读取数据时产生相应的控制逻辑。

3.2 cpld控制逻辑

当并行数据进入板卡后,cpld首先将一部分数据存入锁存器,而将另一部分数据直接存入fifo。但此时必须将写时钟信号wclk进行二分频,以便在一个ad转换周期内完成两次fifo写操作。当fifo数据到达半满时,cpld便向pci9054发出中断申请,并由pci9054将该申请传入计算机。若系统响应该中请,则在中断响应程序内发出读命令,以读取字节数和地址信号等。

pci9054通过lhold申请local总线控制权,而cpld则通过lholda响应,以使pci9054能得到局部总线的控制权。pci9054首先将pci地址窄间映射到本地地址空间,接着启动本地总线的散聚dma周期。cpld收到读信号(lw/r)、地址选通信号(ads)和地址(la16、la17)后便开始传送数据。当la16位为0,la17位为1时,系统将使能后三片fifo的读使能端(ren2),以使后三片fifo数据线上的q0~q31有效而同时也使pci9054的准备好信号(ready)有效,开始数据传送。在最后一个数据传送之前,blast信号有效,之后,cpld将在一个时钟周期后使fifo的读使能(ren1或ren2)无效,从而完成一次数据传送过程。

评论