一种基于FPGA的栈空间管理器的研究和设计

3栈空间管理器设计

为了快速、有效地保护被切换任务的信息,并满足自动检验功能的要求,在栈空间管理器设计中设计了2个逻辑模块,分别为状态控制逻辑模块和地址产生逻辑模块。状态控制逻辑模块主要生成入栈/出栈控制信号和Used信号,地址产生逻辑模块主要生成有效的入栈/出栈地址。基于对栈空间管理器总体结构工作过程的阐述,在Xilinx公司设计的XUPVirtexIIPro系列的芯片上设计一个模拟栈空间管理器,模拟管理8个任务,任务栈的深度为64,宽度为16bit,中断嵌套栈的深度为128,宽度为16bit,容量为10KB的堆栈空间。在设计管理器中,保证管理器快速综合,使占用FPGA的资源尽可能少,存储单元的选择是关键,该系统采用的是FPGA上一个18KB的BlockRAM资源,使用ISE8.2i提供的双端口RAM存储模块的IP核。如果选择其他方法,如用触发器和寄存器搭建存储单元,则综合时间长,且占用大量FPGA的Slices资源。

在实际嵌入式系统应用中,根据系统要求,可计算出栈空间深度和宽度,具体的深度和宽度在VHDL代码中修改即可。

3.1状态控制逻辑模块设计

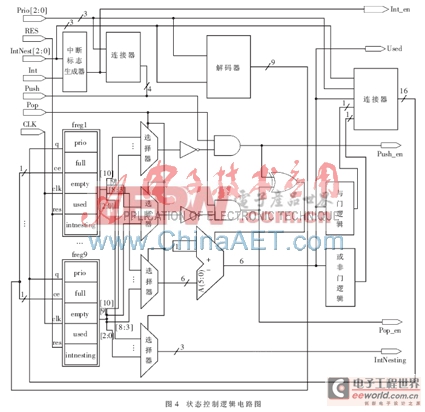

由于状态标志寄存器的空/满状态标志位决定栈空间入栈/出栈操作,所以如何设计空/满状态标志位是关键。为了保护的数据能正确入栈与出栈,防止存储器出现向上溢出或向下溢出,保证在满的情况下,不能进行push操作;在空的状态下,不能进行pop操作。控制信号的产生过程如图4所示。

在状态控制逻辑模块设计时,prio_int信号驱动4个多路选择器,选择对应状态标志寄存器组中的各位段,分别有full信号值、empty信号值、fcount信号值和intNesting信号值。empty/full信号和push/pop信号作为组合逻辑输入信号产生相应的push_en/pop_en有效控制信号,该控制信号决定栈空间是否执行入栈/出栈操作。

在push_en/pop_en控制信号有效的情况下,驱动二进制运算逻辑加/减1,输出运算结果。输出的信号值有3个用途:(1)作为空/满标志状态产生逻辑的输入信号,该信号逻辑产生empty/full信号;(2)写回到fregx对应的fcount位中;(3)作为Used输出信号值,表示当前任务栈或中断嵌套栈的使用情况。

在产生empty、full信号逻辑模块设计时,采用了对输入信号的每一位进行组合逻辑判断的方法,使该信号分两路,一路作为与门组合逻辑的输入信号产生full信号。如果输入信号的每一位都为1,则full信号置1,其他情况置0;另一路作为或门非组合逻辑的输入信号产生empty信号。如果输入信号的每一位都为0,则empty置1,其他情况置0。在整个逻辑模块设计中,采用组合逻辑设计,目的是缩短工作时延,提高系统工作频率。

评论