一种基于FPGA的RFID无线通信系统的实现

1.3.2 SPI硬件设计

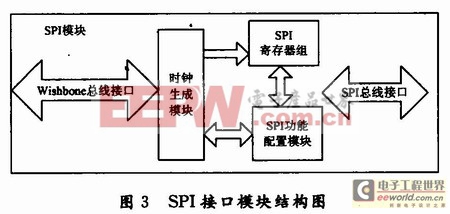

图3是本文无线通信系统中SPI模块的结构图,该系统中的SPI主要由时钟生成模块,SPI寄存器组,SPI功能配置的模块组成,并且通过Wishbone总线与控制器相连,具体设计如下:

时钟生成模块:由于SPI模块是基于FPGA来实现的,而FPGA外部提供的时钟较快(50 MHz或100 MHz),不适合与NRF905的SPI接口进行通信(1 Hz~10 MHz),所以需要分频来使时钟慢下来。但是至于几分频是由SPI功能配置模块来完成的。其次由于SPI协议指出数据可在上升沿或下降沿触发,所以还需要对时钟的上升沿或下降沿进行鉴别(也称抓沿程序),这个功能也由这个模块完成。

SPI寄存器模块:这个模块实现的是一个由16个8位寄存器组成的128位的寄存器组,也就是说通过SPI接口一次性可收发8~128位的串行数据。具体操作由SPI功能配置模块来完成。

SPI功能配置模块:这个模块相当于一个SPI控制器,通过对其寄存器的配置来决定时钟的分频数,收发数据位数,时钟上升沿或下降沿传输数据等,而对这些寄存器的配置是由控制模块完成的。下面就配置寄存器做一些简要说明。

首先介绍控制寄存器:

- 控制寄存器第O位go:是否开始发送。

- 控制寄存器第1位rx_negedge:接收数据是下降沿还是上升沿。

- 控制寄存器第2位tx_negedge:发送数据是下降沿还是上升沿。

- 控制寄存器第3~9位char_len:发送数据的位数(因为SPI是全双工的,所以这实际上也是接收数据的位数)。

- 控制寄存器第10位lsb:是从高位发送还是地位发送。

- 控制寄存器第11位ie:读写完成之后是否发送中断信号。

- 控制寄存器第12位ass:是否自动产生片选信号。

- 分频寄存器:spi_divider_sel。

- 状态寄存器:spi_ctrl_sel。

- 数据寄存器O:spi_tx_sel[0]。

- 数据寄存器1:spi_tx_sel[1]。

- 数据寄存器2:spi_tx_sel[2]。

- 数据寄存器3:spi_tx_sel[3]。

- 片选信号寄存器:spi_ss_sel。

评论