一种基于FPGA的立体视频转换系统研究设计

2.1 DVI输入输出

DVI输入输出控制,一方面根据同步信号采集视频数据;另一方面要根据输入信号生成输出信号,包括行同步(HSYNC)、场同步(VSYNC)、数据有效信号(DE)等。以输入视频信号1 280×1 024@60Hz为例,根据VESA(Video Electronics Standards Association)标准,此时像素时钟fp=108 MHz,每一行信号期间,当DE信号为高电平时,数据有效。于是可以在检测到DE信号的上升沿后开始采集数据,而在DE转为低电平后停止数据的采集。采集的数据写入SRAM,SRAM地址由同步信号解码产生。

为了精确生成输出DVI的同步信号,需要在采集DVI输入数据的同时统计输入信号各个特征脉冲维持的时钟数。图4所示为以行为单位统计场同步信号的参数。输出端在根据统计参数生成DVI同步信号的同时,当输出信号的DE为高电平时,从输出SRAM读取相应的数据送到数据总线。

2.2 数据缓冲

数据缓冲是整个设计的关键。数据的存储缓冲是信号处理中通常会遇到的问题。视频信号的缓冲,由于其数据量大,使得对存储器的容量和速度都提出了比较高的要求。当系统工作在1 600×1 200@60 Hz的最大分辨率时,存储一帧数据所需的容量是d0=1 600×1 200×3 B=5.49 MB,此时的数据率为d=d0×60=329.59 MB/s,这要求存储器具有大容量和足够快的速度。常用的数据缓冲方法有FIFO、双端口RAM和乒乓操作3种。

FIFO的使用非常简单,缺点是只能顺序读写,并且容量较小。双端口RAM可以做随机存取,且速度很快,然而SRAM的价格昂贵,容量通常在几百Kbit到几Mbit大小,所以也不适合做大容量的存储。而SDRAM有容量大且速度较快的优点,所以采用SDRAM的乒乓操作既可以满足视频数据大容量的要求,又能满足速度上的要求,是一种较好的方案。

综合以上方案,同时根据输入输出数据时序上的相似性特点,本文提出了一种时分复用单片SDRAM的方案。该方案用一组SDRAM实现类似“乒乓操作”的帧缓冲效果。

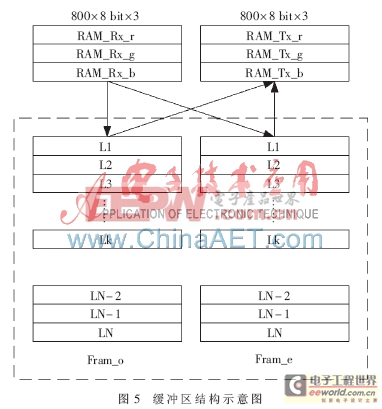

整个存储缓冲的结构如图5所示。输入输出均采用两级缓存的方式。其中第一级缓存可以存储一行数据,采用FPGA片内双端口SRAM实现;二级缓存是可以存放完整两帧数据的DDR SDRAM,作为主存储器。

评论