基于FPGA的灰度形态学滤波器实现

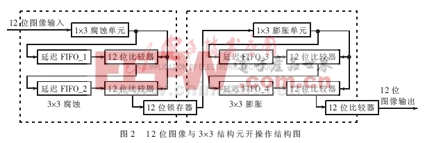

膨胀的结构图与腐蚀的结构图类似,只不过是求相应的最大值。在图1中,A、B二处分别加入非门即可得到膨胀单元的结构图。将腐蚀单元和膨胀单元级联即可得到如图2所示的f与g开操作结构图。整个结构采用流水线方式设计,使串行输入的灰度数据能够得到并行处理,这样就极大地满足了图像处理的实时性要求。

将腐蚀结构图和膨胀结构图次序交换即可得到形态学滤波闭操作结构图。对于不同大小的结构元模板,其结构图与3×3的结构类似,在此不再赘述。

2.3 FPGA实现

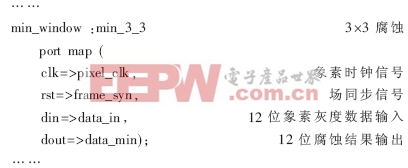

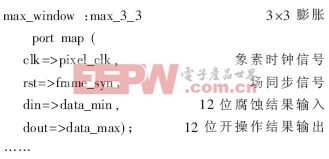

虽然开操作结构图很复杂,但图中实际用到的器件只有12位比较器、12位2选1选择器、深度为256的FIFO以及12位锁存器等。本文选用Xilinx公司的ISE5.2软件为设计平台,以上器件均可以由ISE5.2自带的CORE Generator生成。鉴于开操作的结构特点,整个滤波器采用元件例化的方式设计。求3×3最小值和3×3最大值的部分元件例化VHDL代码如下:

选用XC2S400E芯片,综合后所用主要资源如下:

Number of Slice Flip Flops: 212 out of 9 600 2%

Number of 4 input LUTs: 306 out of 9 600 3%

Number of occupied Slices: 260 out of 4 800 5%

Number of Block RAMs: 4 out of 40 10%

Total equivalent gate count for design: 69 920

评论