利用FPGA实现的任意波形发生器的研究设计

下面就将前5级采用超前进位加法器的32位累加器和宏模块中调用的4位全加器组成的32位相位累加器性能进行比较。

普通流水线累加器的模块是由4位D触发器,5位D触发器和4位全加器作为基本元件,采用原理图输入的方法设计FPGA的流水线累加器。该模块的设计参照流水线累加器结构进行,不同之处在于:由于相位累加器只用高位寻址,所以低位上为了和高位结果同时输出而做延时作用的D触发器件均被去掉了。这样做的结果是,相位累加器输出的低20位会因为提前输出而混乱,但是由于高12位的输出一定是正确的,这样做既节省了资源,对结果又没有任何影响。仿真结果证明假如不用流水线结构,32 bit相位累加器工作频率最高达到约25 MHz。消耗的资源是82个LEs,而用了8级流水线结构后,编译工作频率最高达到了约317.79 MHz,资源消耗为186个LEs。可见在资源上的消耗换来了在性能上的极大提高。

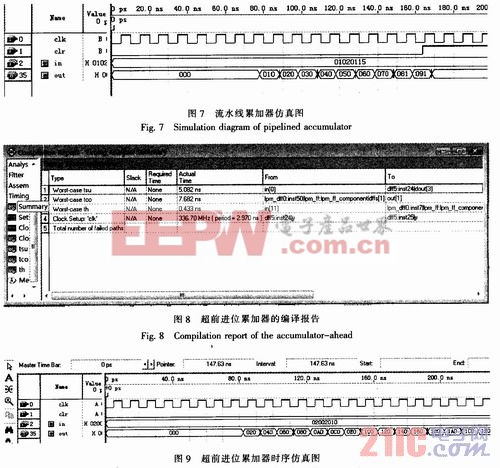

流水线累加器的时序仿真如图7所示:可以看出当输入数据确定后,输出结果要经过8个时钟周期的延时后输出,这是因为采用了8级流水结构。采用多少级流水结构,输出就会延时多少个周期。同时也说明,对于输入数据切换来说,该系统会有8个时钟周期的延时,这是累加器采用流水线结构所不可避免的后果。事实上目前许多DDS专用芯片由于也采用流水线结构,所以本身也存在这样的问题。由于8个时钟周期的延时与系统时钟相比,实际上还是很小的,在一般的应用场合下也是可以接受的。由于输出的低20位未用,被省略了,只用了输出的高12位,所以仿真波形中只有高12位的输出结果。从输出结果来看,高12位的输出值是没有错误的,与设计思想吻合。

下面介绍超进位流水线累加器的构成,比较流水线累加器内部结构图和超前进位加法器的32位相位累加器的结构图,可以看出两个图的区别,经过编译以后的报告如图8所示,可以看出经过改进后,编译的最大工作频率提高到了336.7 MHz。比单纯的流水线累加器提高了将近20 MHz。

图9是其时序仿真图,从图上可以看出,其值完全和功能仿真一致。

评论