4 半整数分频器设计

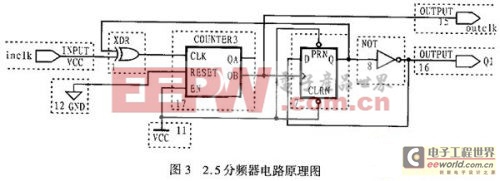

现通过设计一个分频系数为2.5的分频器给出用FPGA设计半整数分频器的一般方法。该2.5分频器由模3计数器、异或门和D触发器组成。

图3 2.5分频器电路原理图

4.1 模3计数器

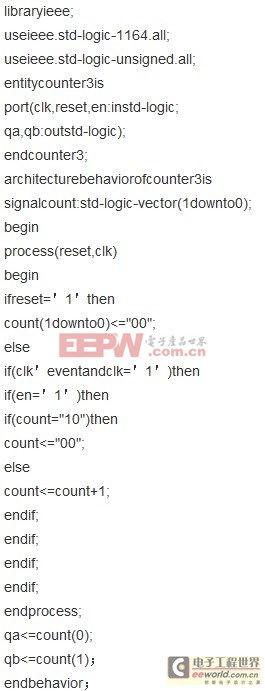

该计数器可产生一个分频系数为3的分频器,并产生一个默认的逻辑符号COUNTER3。其输入端口为RESET、EN和CLK;输出端口为QA和QB。下面给出模3计数器VHDL描述代码:

任意模数的计数器与模3计数器的描述结构完全相同,所不同的仅仅是计数器的状态数。上面的程序经编译、时序模拟后,在MAX+PLUSII可得到如图2所示的仿真波形。

分频器相关文章:分频器原理

评论