基于ARM的快速原型化平台的实现

可编程器件如CPLD和FPGA,可以在系统编程,修改连接只需要修改相应的控制程序即可,非常方便灵活。CPLD成本低,运行速度快,但是集成度比较低。FPGA集成度高,可以实现CPLD很难实现的复杂的逻辑功能,例如内嵌逻辑分析仪程序,获取必要的信号,完成系统在线测试。FPGA另外一个优势就是可以动态配置,例如系统上电时配置自检程序,自检通过后再配置实际工作的程序。最后,在FPGA里面嵌入CPU软核,进行SOC的开发。所以可编程互连模块选用FPGA来组成。

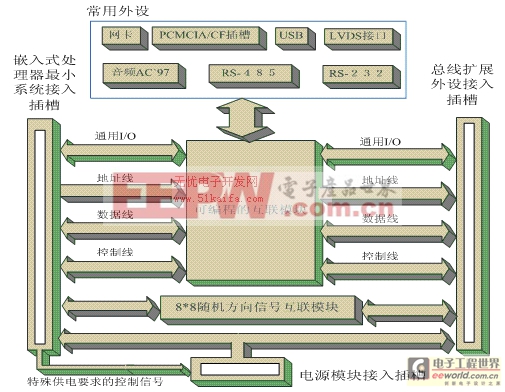

为了确定可编程互连模块的插入位置,再来分析图2嵌入式系统的结构。

最小系统决定了整个系统的处理能力,是整个系统的核心。常用的嵌入式处理器的时钟周期已经高达400MHz,并且会进一步发展。连接处理器的总线速度和存储器芯片的速度也超过了100MHz。FPGA引脚到引脚的延时是几个纳秒的数量级,所以FPGA模块的插入会降低整个系统的处理速度。故在处理器和存储器之间不能插入FPGA模块。外设可以使得嵌入式系统和实际应用环境进行通信和交互操作。通常外设已经高度模块化并且相互独立,在外设之间几乎不会有柔性连接的要求,而且处理器和外设之间的数据通信速度比最小系统的运行速度要慢很多。因此,用互连模块取代最小系统和外设之间的直接物理连接是切实可行的。

按照这种思路,设计出了如图3所示的快速原型化平台。

图3(快速原型化平台)

图3中,可编程互连模块是快速原型化平台的核心部分。常用的外设部分包括:网卡,USB接口,LVDS接口,RS-232接口,RS-485接口,音频AC`97接口,PCMCIA/CF卡接口。这些常用外设就是前文提到的可重复利用的模块。由于嵌入式处理器的总线、通用I/O、专用I/O和各种外设都连接在可编程互连模块上,因此不同的嵌入式处理器只需要设计最小系统即可,然后将该最小系统接入快速原型化平台,利用这个平台提供的外设进行系统调试。

以上设计的快速原型化平台,不仅考虑了当前嵌入式硬件系统的发展特点即嵌入式处理器种类多,外设种类相对较少,接口标准趋于统一,同时又充分体现了可测性、灵活性、模块化的设计思想。

3 随机方向信号的可配置互连

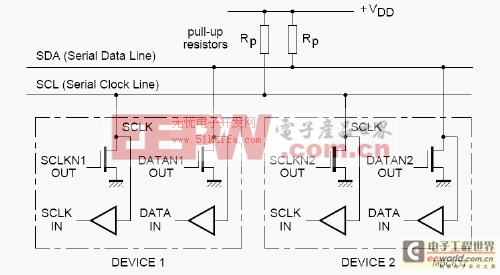

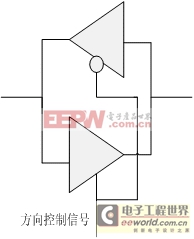

常见的信号传输方向不管是单向的还是双向的,都可以预先确定。例如,数据总线是双向的,读或者写是完全确定的,可以通过读写信号来控制数据的传输的方向。但是有一类特殊的总线,例如I2C,它是多主/从的通信总线。如图4所示,如果设备1发起通信,则SCL上的信号传输方向是从设备1到设备2,如果是设备2作主设备发起通信,则SCL的上的信号传输方向刚好相反。系统设计中要求总线上可以双向传输信号。FPGA内部由一系列的逻辑门组成,如果I2C 信号通过FPGA来连接的话,就不能正常工作。这是因为,双向传输可以等效视为由两个反并联的门来实现(如图5,用方向控制信号来确定实际的传输方向)。但是,I2C信号,没有明确的方向控制信号,也就无法正确地通过图5 所示结构的电路。

图4(I2C总线)

图5(双向信号传输)

如果直接布线或者跳线来连接I2C信号,就可以保证I2C正常工作,但是,这就和快速原型化平台可配置互连的灵活性相违背,所以提出以下方案。 I2C信号不经过FPGA来配置连接,而是通过基于MOSFET的数据开关。目前,市场上常用的点到点任意方向的MOSFET开关并不能直接使用。因为常见的结构是一路到多路或者多路到一路。利用CPLD来控制选通,多路并联就可以组成8X8的点到点的随机方向的可配置连接。如图6,是一路到八路的数据开关的内部结构。

评论