基于FPGA的高速数据采集系统的设计方案

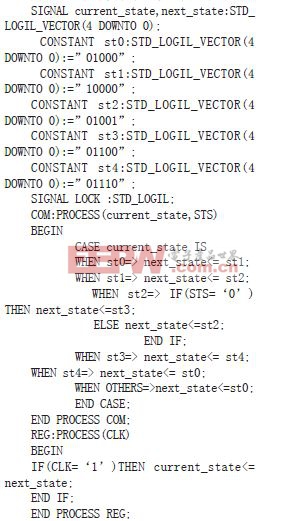

用VHDL语言来实现状态机,其原程序:

然后在Quartus Ⅱ 中进行仿真,仿真如图2所示:

4.2.2 FIFO模块设计

利用FPGA中的EAB/ESB等嵌入式模块构成的LPM宏功能模块来生成LPM_FIFO.其编辑定制方法:

(1)进入QuartusⅡ,选择菜单File->TOOL->Megawizard Plug-In Manager,选择Create a new custom megafunctionvariation,选择FIFO.

(2)选择FIFO数据位宽度为12,深度为512.

(3)选择FIFO的端口:12位数据输入输出端口data[120]和q[120];对clock同步的数据写入和读出请求wrreq和rdreq;异步清零aclr;存储数据溢出信号full.

5.结论

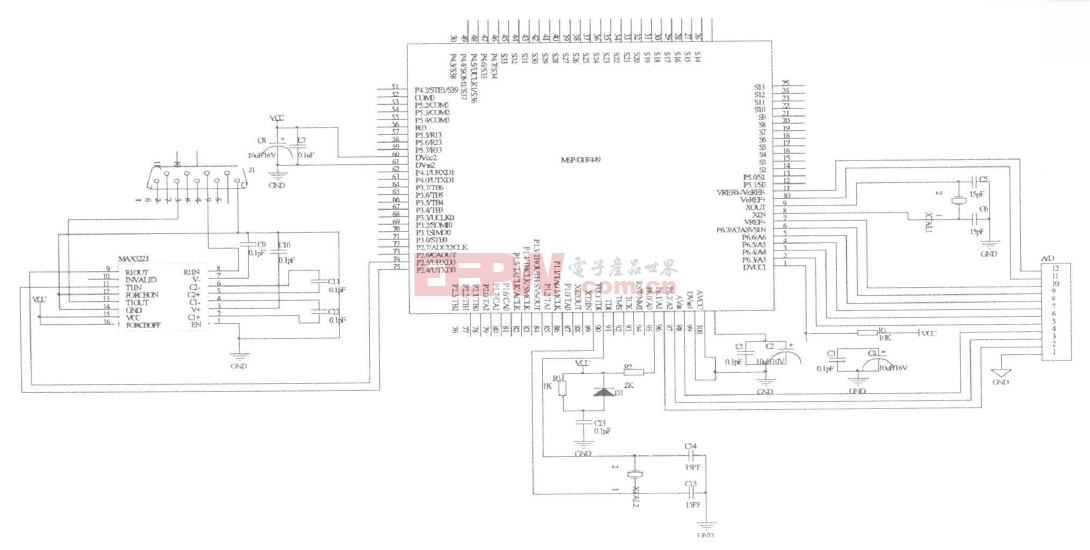

本文完成高速、多通道的数据采集系统的FPGA设计。利用VHDL语言对FPGA进行设计,并在QuartusⅡ中进行系统仿真和验证。

由FPGA在线编程的特点,可以依据现场的具体情况,对FPGA的内部配置进行修改,进一步增加了系统应用的灵活性,因此该系统是一种比较理想的实时高速数据采集方案

评论