基于AMBA-AHB总线的SDRAM控制器的计方案

SDRAM上电后必须按一种确定的方式初始化。在上电稳定后100 μs时间内存储器不接受除NOP以外的任何命令。当100 μs过后,通过控制器向SDRAM所有bank 发出预充电(Precharge)命令[8],使SDRAM 所有bank进入待机状态。之后,要对SDRAM 连续执行两个自动刷新操作,使SDRAM 芯片内部的刷新及计数器进入正常运行状态。两个刷新周期完毕之后,开始对SDRAM 的模式寄存器(Mode Register)进行操作,模式寄存器用来决定SDRAM将以何种工作模式工作。整个初始化过程如图2所示。

3 SDRAM 控制器与AMBA-AHB 总线的关系

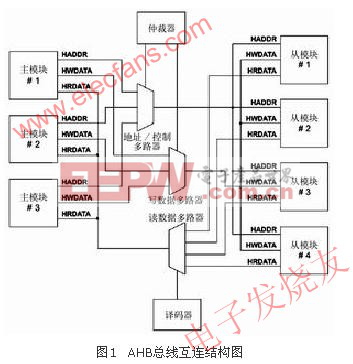

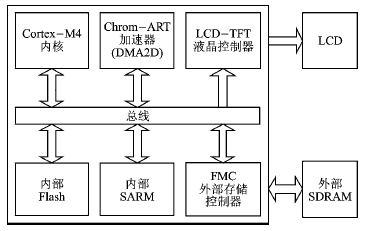

本设计基于AMBA-AHB总线的slave模块,SDRAM控制器处在片内AHB 总线与片外存储设备之间,作为一个从机挂在AHB总线上。它一边需要通过AHB总线接口模块与AHB总线通信,因此必须符合AHB总线标准;另一边又需要给外部存储设备提供控制信号,以实现对外部存储设备的读写操作。控制器接收来自总线主设备的符合AMBA-AHB 总线规范的数据传输请求,产生正确的读写控制信号给SDRAM 存储器,以完成总线的数据传输请求。

AMBA 2.0总线为嵌入式微控制器定义了一套片上总线标准,因此本设计是独立设计的基于该规范的外围IP.

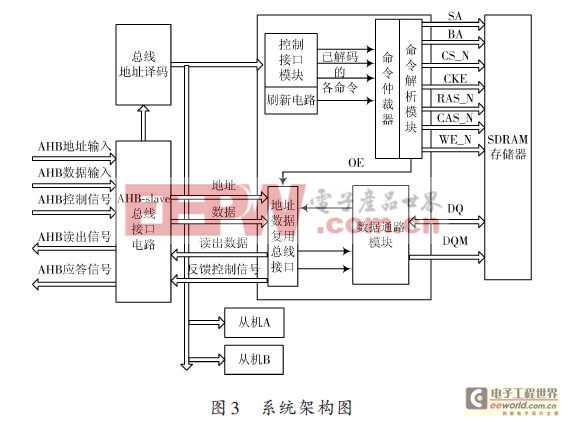

4 SDRAM 控制器系统设计架构

SDRAM 控制器与AHB 总线接口在整个系统中的连接关系如图3所示。

4.1 AHB-slave总线接口电路

AHB-slave总线接口电路用来实现SDRAM 控制逻辑与AHB-master之间的信号传输。

按照AMBA 总线规范要求,AHB 总线从设备(slave)在总线时钟上升沿,HREADY信号(由从设备发出)为高的情况下,必须锁存来自AHB总线的总线控制信号、数据信号、地址信号等,以供内部译码模块以及其他各模块使用。

评论