高速PCI信号采集卡设计与实现综合实例之: FPGA内部结构设计

13.6FPGA内部结构设计

13.6.1构框图

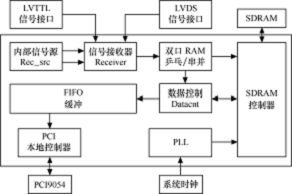

基于FPGA及PCI9054的信号采集卡的核心设计部分是FPGA内部结构的逻辑设计。如图13.15所示为本系统FPGA内部结构框图。

本文引用地址:https://www.eepw.com.cn/article/201706/348784.htm其中,信号接收器是接收采集信号的模块,对LVTTL信号接口和LVDS信号接口输入的信号进行分析,并将获得的信号送入下一个模块。

内部信号源是一个用于测试的模块。通过产生一个已知的有序的信号序列送至信号接收器,最终进入主机后进行检测,即可得知整个传输过程的正确性。

双口RAM用于实现信号的串并转换,使输入的信号转换成32位数据位宽,同时实现时钟域的转换。另外通过乒乓操作实现数据的有序存取。

图13.15FPGA内部结构框图

数据控制模块用于产生双口RAM和SDRAM控制器的地址总线、数据总线和控制总线,是双口RAM模块与SDRAM控制器的桥梁。实现双口RAM至SDRAM控制器正确的数据转移。同时,数据控制模块还负责从SDRAM控制器读取数据,并送至FPGA内的FIFO缓冲区中,用于PCI总线交互。

SDRAM控制器是FPGA内用于外部SDRAM控制的模块。

PCI本地控制器是FPGA内用于控制PCI9054本地总线交互的模块。

PLL是AlteraFPGA内提供的模拟延迟锁相环模块,可以实现系统时钟的倍频、分频及延迟等时钟控制操作。通过该模块可以实现系统内不同时钟域的时钟分配。

13.6.2设计方法

在实际的设计中,主要通过自行编写模块、调用宏模块和引用开源模块3种方式来实现模块的设计。

1.自行编写模块

自行编写模块就是完全通过自行编写的逻辑完成模块的设计,可以使用硬件编程语言、状态机、电路图等方式实现。

本设计中的PCI本地控制器、信号接收器、内部信号源、数据控制等模块都是使用Verilog硬件语言自行编写设计的。

2.调用宏模块

在逻辑设计中,Altera已经为设计者提供了丰富的基本逻辑组件的模块。设计者只需使用宏模块向导进行调用,配置相应的参数,即可得到符合设计需求的模块。

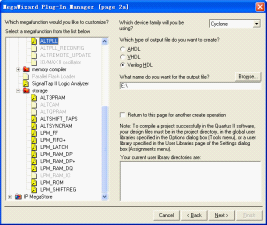

本设计中的双口RAM、PLL及FIFO缓冲模块正是通过调用CycloneFPGA支持的相应的LPM_RAM_DP、ALTPLL和LPM_FIFO+宏模块实现的。如图13.16所示为Altera宏模块向导管理器界面。

图13.16Altera宏模块向导管理器

3.引用开源模块

除了设计者自行编写模块及宏模块向导管理器中提供的模块以外,设计者还可以引用开源的模块加入到系统的设计中。开源的模块往往是一些厂家对一些常见的外围器件提供的控制模块。

本设计中使用的SDRAM控制器正是引用了成熟的开源模块进行的设计,Altera为SDRAM控制器给出了白皮书和开源模块。设计者只需将该开源模块引用至系统的设计中,进行一定的修改即可使用。

评论