高速PCI信号采集卡设计与实现综合实例之:样机的调试方法和技巧

13.8样机的调试方法和技巧

不管是复杂的电子系统还是简单的电路,样机的调试都是有一些基本步骤的。对于本案例的信号采集设备同样如此。

最先进行的就是电源系统的调试,包括是否有短路、断路,是否有虚焊,各电压系统是否正常,电源模块输出电流是否足够驱动负载等。只有电源系统正常工作,才能谈得上实现系统功能。

完成了电源系统的调试后,PCI信号采集卡的下一个工作就是对PCI954进行配置。用户可以通过编程器或者PLXMon工具在线进行烧写。这个配置过程保证主机操作系统能够识别出硬件设备。

主机能够正确地识别硬件设备后,需要进行设备驱动程序的安装。

通过上述步骤,主机已经可以正确地识别设备,并为用户提供了可供操作的API接口。接下来要做的调试工作就是硬件工程师要完成的FPGA逻辑设计和软件工程师要完成的应用软件设计。但这两部分并不能绝对分开进行设计,因为不管是对设备的I/O操作还是DMA操作都需要进行地址空间映射,因此都需要在软件和硬件上进行相应的设计。

在本系统的FPGA调试和软件联调中,我们使用了两个简单的例子来验证系统是否能够正常的工作。一个是直接用FPGA控制的跑马灯实例,另一个是通过应用软件控制的跑马灯实例。

13.8.1没有PCI控制的跑马灯

本实例仅用FPGA内部逻辑对LED进行控制,实现跑马灯。通过本实例可以检验FPGA的两种配置模式是否正常工作,同时可以学习使用QuartusII软件开发和配置FPGA的流程。

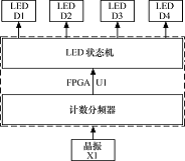

如图13.23是本实例的系统框图。

图13.23跑马灯系统框图

其中计数分频器是通过计数器将晶振的40MHz时钟进行分频,产生的低频时钟作为LED状态机的控制时钟。LED状态机使用4个状态分别表示4个LED的亮灭,状态转换通过状态机的时钟上升沿触发,实现跑马灯。

下面是这个实例FPGA内的主要Verilog源代码。

//--计数分频-------------------------------------

always@(posedgeclkin)

count=count+1; //分频计数器

assignclk=count[24]; //状态机时钟

//--LED控制--------------------------------

always@(posedgeclk)begin

case(state)//跑马灯状态控制量

2d0: led=4b0001; //D1亮

2d1: led=4b0010; //D2亮

2d2: led=4b0100; //D3亮

2d3: led=4b1000; //D4亮

endcase

state=state+1;//跑马灯状态变化

end

13.8.2基于PCI控制的跑马灯

本实例使用应用程序通过PCI总线(PCI9054)来对FPGA内部逻辑参数进行配置,实现对LED的控制。通过本实例可以检验开发板的驱动以及PCI的实时控制,同时学习应用程序和PCI9054进行通信的方法。

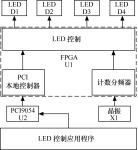

如图13.24所示为本实例的系统框图。

图13.24基于PCI控制的跑马灯系统框图

其中PCI本地控制器实现与PCI9054的接口通信,获取LED控制应用程序发出的触发信号。LED控制器包含LED状态机并接受PCI本地控制器的触发信号,通过判别LED触发的类型决定启动单个LED控制或LED状态机。

下面是这个范例FPGA内的主要Verilog源代码。

//--计数分频-------------------------------------

always@(posedgeclkin)

count=count+1; //分频计数器

assignclk=count[24]; //状态机时钟

//--LED控制--------------------------------

always@(posedgeclk)begin

case(LEDByControl) //状态控制量

8d1: led=4b0001; //PCI控制D1亮

8d2: led=4b0010; //PCI控制D2亮

8d3: led=4b0100; //PCI控制D3亮

8d4: led=4b1000; //PCI控制D4亮

8d5: case(state) //跑马灯状态控制量

2b00: led=4b0001; //跑马灯D1亮

2b01: led=4b0010; //跑马灯D2亮

2b10: led=4b0100; //跑马灯D3亮

2b11: led=4b1000; //跑马灯D4亮

endcase

default:led=4b0000; //跑马灯全灭

endcase

state=state+1; //跑马灯状态变化

end

//--PCI本地控制器-------------------------------

always@(posedgeclkin)

lholda=lhold; //PCI本地总线占用请求及应答

always@(posedgeclkinornegedgelrst)begin

if(!lrst)begin//PCI9054复位

readyflag=1b0;

LEDByControl[7:0]=8b0;

end

elseif(!adslwrblastla[13:0]==14b1)

readyflag=1b1;//开始发起LED控制字IO配置

elseif(adslwrblastreadyflag==1b1la[13:0]==14b1)

readyflag=1b1;//捕获发起操作

elseif(adslwr!blastreadyflag==1b1la[13:0]==14b1)begin

LEDByControl[7:0]=ld[31:24];//进行LED控制字IO配置操作

readyflag=1b0;

end

else begin

LEDByControl[7:0]=LEDByControl[7:0];//保持LED控制字

readyflag=1b0;

end

end

在进行FPGA的逻辑设计时,采用一种叫做虚拟逻辑分析仪的技术,可以增强我们诊断系统的能力。AlteraFPGA提供的虚拟逻辑分析仪称为SignalTap,Xilinx中也有同样功能的产品称为ChipScope。

SignalTapII逻辑分析仪是Altera第二代系统级调试工具,能够获取、显示可编程片上系统(SOPC)的实时信号,帮助工程师在其系统设计中观察硬件和软件的交互作用。在可编程逻辑市场上,SignalTapII逻辑分析仪专用于QuartusII软件,与其他嵌入式逻辑分析仪相比,它支持的通道数最多,抽样深度最大,时钟速率最高。

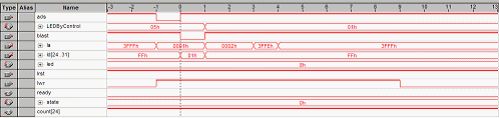

如图13.25所示为控制其中一个LED时的PCI本地时序图。

图13.25控制1个LED的PCI本地时序图

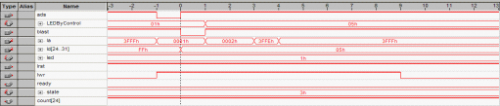

如图13.26所示为控制4个LED进行跑马灯时的PCI本地时序图。

图13.26控制4个LED跑马灯的PCI本地时序图

评论